# Components and materials

Part 7 September 1971

Circuit blocks

# **COMPONENTS AND MATERIALS**

Part 7

September 1971

| Circuit blocks 100 kHz Series                | Α |  |

|----------------------------------------------|---|--|

| Circuit blocks 1-Series                      | В |  |

| Circuit blocks for ferrite core memory drive | С |  |

| Circuit blocks 10-Series                     | D |  |

For comprehensive contents list see back

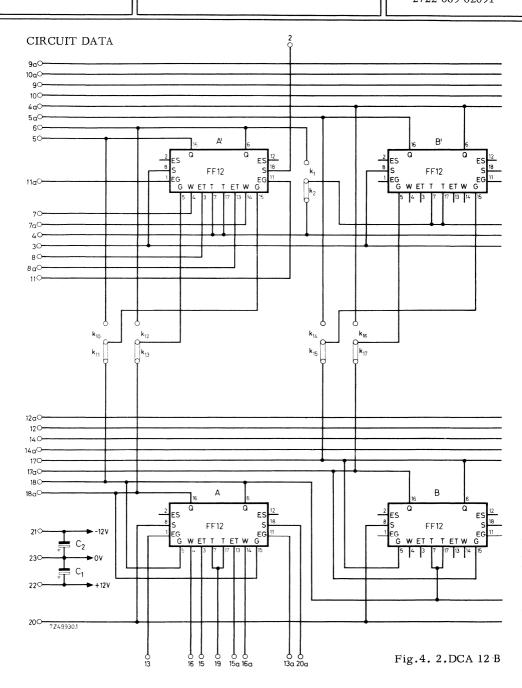

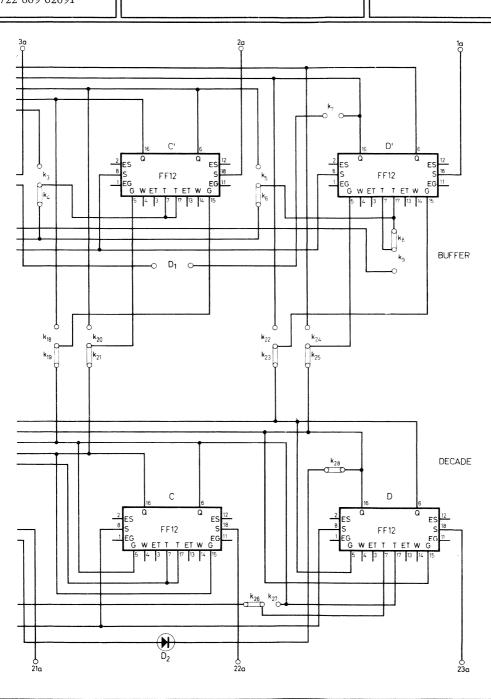

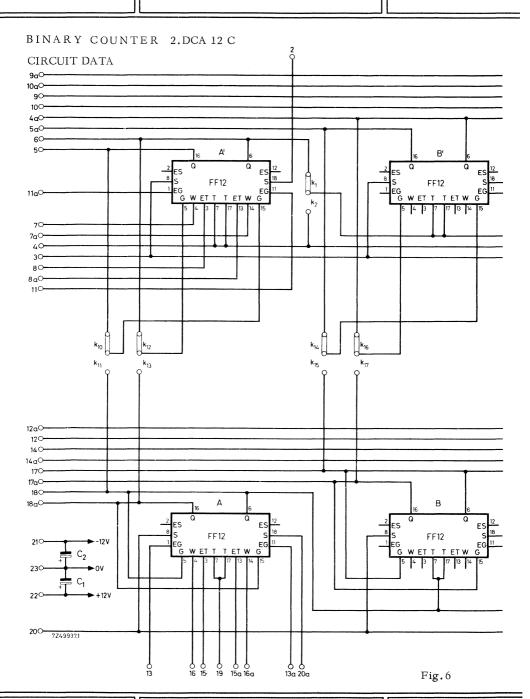

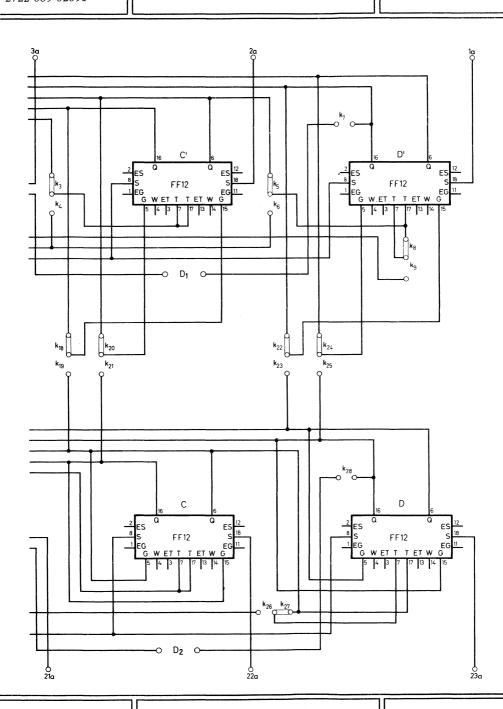

## DATA HANDBOOK SYSTEM

To provide you with a comprehensive source of information on electronic components, subassemblies and materials, our Data Handbook System is made up of three series of handbooks, each comprising several parts.

The three series, identified by the colours noted, are:

**ELECTRON TUBES** (9 parts)

BLUE

**SEMICONDUCTORS AND INTEGRATED CIRCUITS (5 parts)**

RED

**COMPONENTS AND MATERIALS** (7 parts)

GREEN

The several parts contain all pertinent data available at the time of publication, and each is revised and reissued annually; the contents of each series are summarized on the following pages.

We have made every effort to ensure that each series is as accurate, comprehensive and up-to-date as possible, and we hope you will find it to be a valuable source of reference. Where ratings or specifications quoted differ from those published in the preceding edition they will be pointed out by arrows. You will understand that we can not guarantee that all products listed in any one edition of the handbook will remain available, or that their specifications will not be changed, before the next edition is published. If you need confirmation that the pusblished data about any of our products are the latest available, may we ask that you contact our representative. He is at your service and will be glad to answer your inquiries.

# **ELECTRON TUBES (BLUE SERIES)**

This series consists of the following parts, issued on the dates indicated.

Part 1

January 1971

Transmitting tubes (Tetrodes, Pentodes)

Associated accessories

Part 2

March 1971

Tubes for microwave equipment

Part 3

March 1970

Special Quality tubes

Miscellaneous devices

Part 4

**April 1971**

Receiving tubes

Part 5

May 1971

Cathode-ray tubes Photo tubes Camera tubes Photoconductive devices Associated accessories

Part 6

June 1971

Photomultipliers tubes Channel electron multipliers Scintillators Photoscintillators Radiation counter tubes Semiconductor radiation detectors Neutron generator tubes Photo diodes Associated accessories

Part 7

July 1971

Voltage stabilizing and reference tubes Counter, selector, and indicator tubes Trigger tubes Switching diodes

Thyratrons

Ignitrons

Industrial rectifying tubes

High-voltage rectifying tubes

Part 8

August 1971

T.V. Picture tubes

Part 9

January 1971

Transmitting tubes (Triodes)

Tubes for R. F. heating (Triodes)

Associated accessories

August 1971

# SEMICONDUCTORS AND INTEGRATED CIRCUITS (RED SERIES)

This series consists of the following parts, issued on the dates indicated.

### Part 1 Diodes and Thyristors

September 1971

General

Signal diodes

Variable capacitance diodes

Voltage regulator diodes

Rectifier diodes

Thyristors, diacs, triacs Rectifier stacks Accessories Heatsinks

### Part 2 Low frequency; Deflection

October 1970

General

Low frequency transistors (low power)

Low frequency power transistors

Deflection transistors Accessories

### Part 3 High frequency; Switching

November 1970

General High frequency transistors Switching transistors Accessories

### Part 4 Special types

December 1970

General

Transmitting transistors

Microwave devices

Field effect transistors

Dual transistors

Microminiature devices for

thick- and thin-film circuits

Beam lead devices for thick- and thin-film circuits Photo devices Accessories

# Part 5 Integrated Circuits

March 1971

General

Digital integrated circuits

DTL (FC family)

TTL (FJ family)

MOS (FD family)

Linear integrated circuits

# **COMPONENTS AND MATERIALS (GREEN SERIES)**

This series consists of the following parts, issued on the dates indicated.

# Part 1 Circuit Blocks, Input/Output Devices, October 1971 Electro-mechanical Components \*), Peripheral Devices

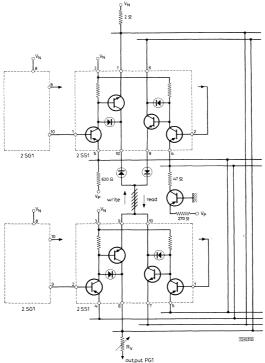

Circuit blocks 40-Series Counter modules 50-Series Norbits 60-Series, 61-Series Circuit blocks 90-Series Input/output devices

Electro-mechanical components \*)

Peripheral devices

### Part 2 Resistors, Capacitors

Fixed resistors Variable resistors Non-linear resistors Ceramic capacitors **December 1970**Polyester, polycarbonate, polystyrene,

paper capacitors Electrolytic capacitors Variable capacitors

## Part 3 Radio, Audio, Television

FM tuners

Coils \* \*)

Piezoelectric ceramic resonators

and filters

Loudspeakers

# February 1971

Audio and mains transformers Television tuners Components for black and white television Components for colour television Deflection assemblies for camera tubes

# Part 4 Magnetic Materials, Piezoelectric Ceramics

April 1971

Ferrites for radio, audio and television Small coils, assemblies and assembling parts Ferroxcube potcores and square cores Ferroxcube transformer cores Piezoxide Permanent magnet materials

# Part 5 Memory Products, Magnetic Heads, Quartz Crystals, June 1971 Microwave Devices, Variable Transformers

Ferrite memory cores Matrix planes, matrix stacks Complete memories Magnetic heads Quartz crystal units, crystal filters Isolators, circulators Variable mains transformers

# Part 6 Electric Motors and Accessories, Timing and Control Devices

August 1971

Stepper motors Small synchronous motors Asynchronous motors Small d.c. motors

Tachogenerators and servomotors

Indicators for built-in test equipment

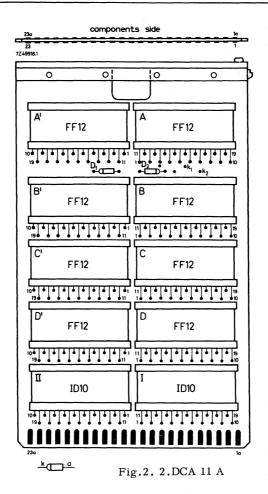

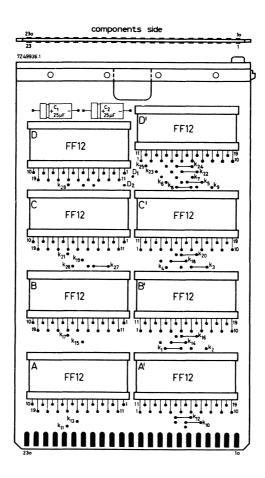

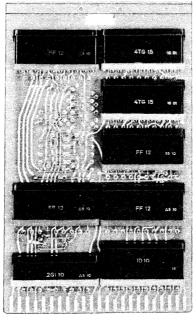

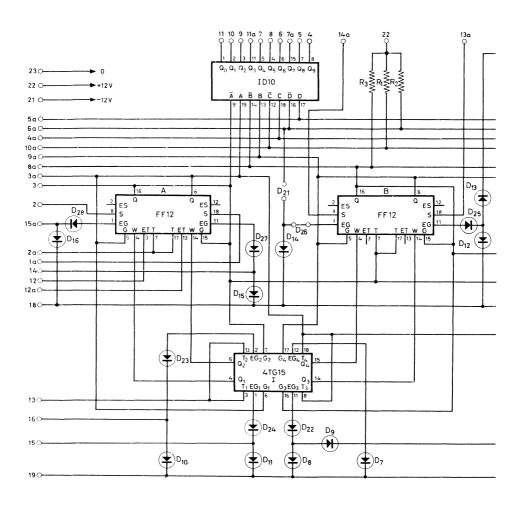

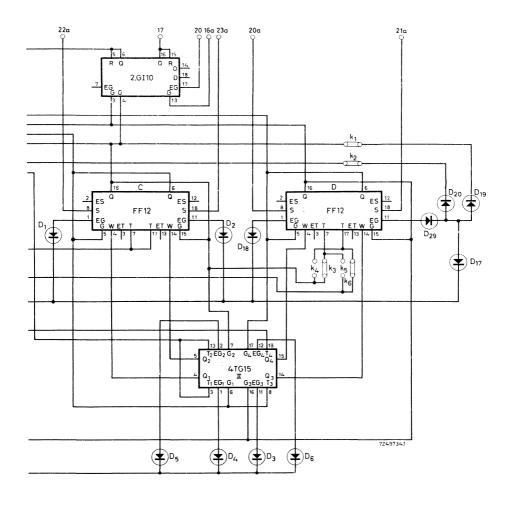

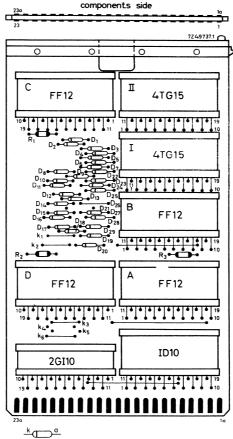

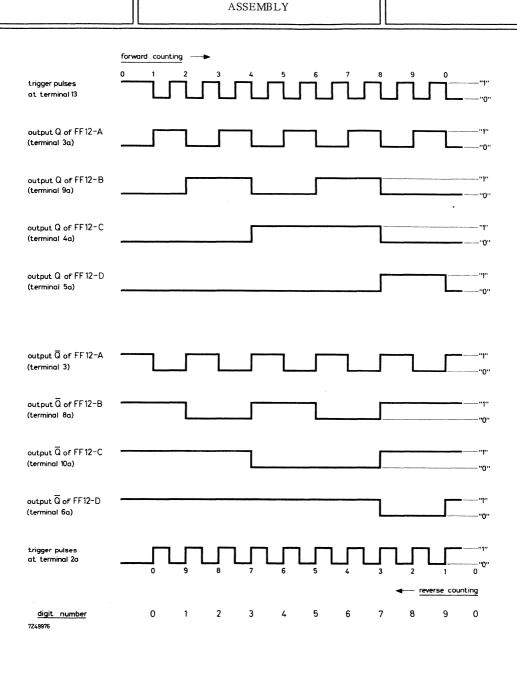

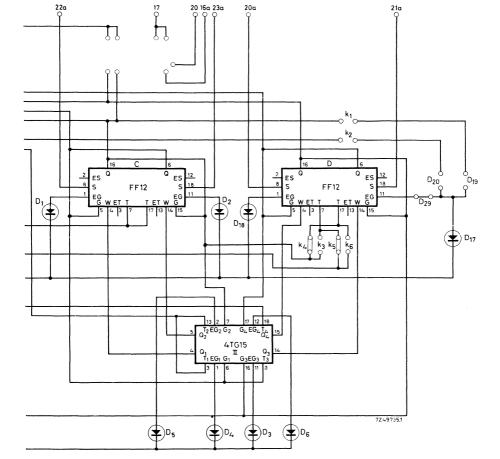

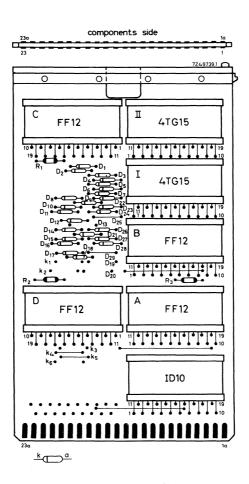

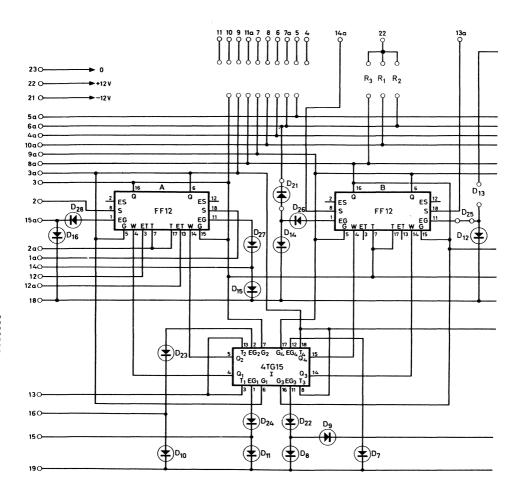

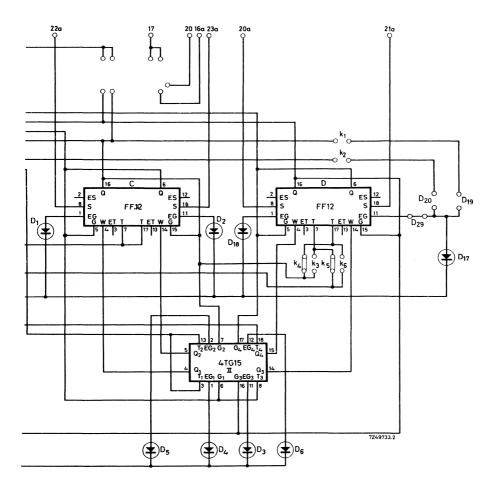

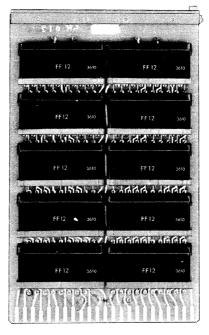

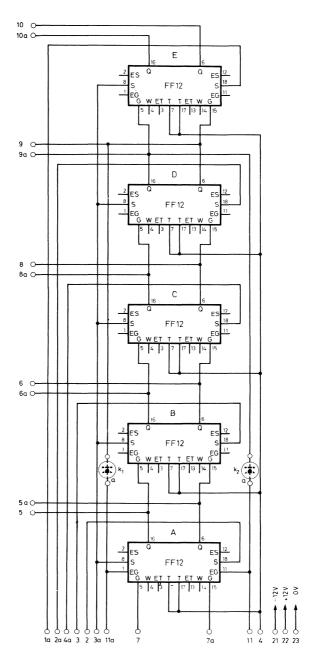

### Part 7 Circuit Blocks

Circuit blocks for ferrite core memory drive

Circuit blocks 100kHz Series Circuit blocks 1-Series Circuit blocks 10-Series

\*) From October 1971 published in Part 1 instead of Part 5.

\*\*) Also included (under "Small coils, etc.") in Part 4.

September 1971

September 1971

### Technology relating to the products described in this publication is shared by the following companies.

Argentina

FAPESA I.y.C. Melincué 2594 Tel. 50-9941/8155 **BUENOS AIRES**

Australia

Philips Industries Ltd. Miniwatt Electronics Division 20, Herbert St. Tel. 43-2171 ARTARMON, N.S.W.

Austria WIVEG Zieglergasse 6 Tel. 93 26 22 A1072 VIENNA

Belgium M.B.L.E. 80, rue des Deux Gares Tel. 23 00 00 1070 BRUSSELS

Brazil IBRAPE S.A. Av. Paulista 2073-S/Loja

Tel. 278-1111 SAO PAULO

Canada Philips Electron Devices 116, Vanderhoof Ave. Tel. 425-5161

TORONTO 17, Ontario

Philips Chilena S.A Av. Šanta Maria 0760 Tel. 39-40 01 SANTIAGO

Colombia SADAPE S.A

Calle 19, No.5-51 Tel. 422-175 BOGOTA D.E. 1

Miniwatt A/S Emdrupvej 115A Tel. (01) 69 16 22 DK-2400 KØBENHAVN NV

Finland

Denmark

Oy Philips A.B. Elcoma Division Kaivokatu 8 Tel. 10 915 HELSINKI 10

France R.T.C.

La Radiotechnique-Compelec Avenue Ledru Rollin 130 Tel. 357-69-30 PARIS 11

Germany VALVO G.m.b.H.

Valvo Haus Burchardstrasse 19. Tel. (0411) 3296-1 2 HAMBURG 1

Philips S.A. Hellénique Elcoma Division 52, Av. Syngrou Tel. 915.311 ATHENS

Hong Kong

Philips Hong Kong Ltd. Components Dept St. George's Building 21st Fl. Tel. K-42 82 05 HONG KONG

India

INBELEC Div. of Philips India Ltd. Band Box House 254-D, Dr. Annie Besant Road Tel. 45 33 86, 45 64 20, 45 29 86 Worli, Bombay 18 (WB)

Indonesia

P.T. Philips-Ralin Electronics Elcoma Division Djalan Gadjah Mada 18 Tel. 44 163 DJAKARTA

Ireland

Philips Electrical (Ireland) Ltd. Newstead, Clonskeagh Tel. 69 33 55 **DUBLIN 14**

Italy

Philips S.p.A. Sezione Elcoma Piazza IV Novembre 3 Tel. 69 94 MILANO

Japan

NIHON PHILIPS 32nd Fl., World Trade Center Bldg. 5, 3-chome, Shiba Hamamatsu-cho Minato-ku, Tel. (435) 5204-5 TOKYO

Mexico

Electrónica S.A. de C.V. Varsovia No.36 Tel. 5-33-11-80 MEXICO 6, D.F.

Netherlands

Philips Nederland N.V. Afd. Elonco Boschdijk, VB Tel. (040) 43 33 33 **EINDHOVEN**

New Zealand

EDAC Ltd. 70-72 Kingsford Smith Street Tel. 873 159 WELLINGTON

Norway

Electronica A/S Middelthunsgate 27 Tel. 46 39 70 OSLO 3

Peru

CADESA Jr. Ilo, No. 216 Appartado 10132 Tel. 27 7317 LIMA

Portugal

Philips Portuguesa S.A.R.L. Rua Joaquim Antonio de Aguiar 66 CARACAS Tel. 68 31 21/9 LISBOA

South Africa

EDAC (PTY) Ltd. South Park Lane New Doornfontein Tel. 24/6701-2 **JOHANNESBURG**

Spain

COPRESA S.A. Balmes 22 Tel. 232 66 80 BARCELONA 7

Sweden

ELCOMA A.B. Lidingövägen 50 Tel. 08/67 97 80 10250 STOCKHOLM 27

Switzerland Philips A.G. Edenstrasse 20 Tel. 051/44 22 11

CH-8027 ZUERICH

Taiwan

Philips Taiwan Ltd. San Min Building, 3rd Fl. 57-1, Chung Shan N. Road Section 2 Tel. 553 101 TAIPFI

Turk Philips Ticaret A.S. **EMET Department** Gumussuyu Cad. 78-80 Tel. 45.32.50 Beyoglu, ISTANBUL

United Kingdom

Mullard Ltd. Mullard House Torrington Place Tel. 01-580 6633 LONDON WC1E 7HD

United States

Amperex Electronic Corp. Electron Tubes Div. Tel. 516 WE 1-6200 HICKSVILLE N.Y. Sem. and Microcircuits Div. Tel. 401-762-9000 SLATERSVILLE R.I. 02876 Electronic Components Div. Tel. 516-234-7000 HAUPPAUGE N.Y.

Ferroxcube Corp.

(Memory Products) P.O. Box 359 Tel. (914) 246-2811 SAUGERTIES, N.Y. 12477

Uruguay

Luzilectron S.A. Rondeau 1567, piso 5 Tel. 9 43 21 MONTEVIDEO

Venezuela

C.A. Philips Venezolana Elcoma Department Colinas de Bello Monte Tel. 72.01.51

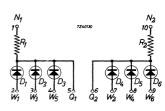

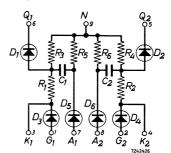

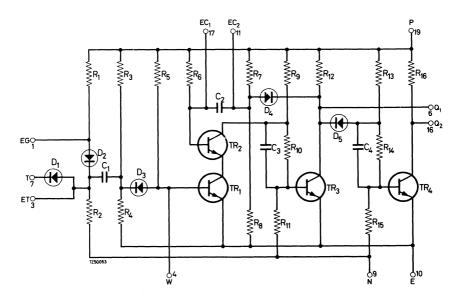

# Circuit blocks 100 kHz Series

# INTRODUCTION

A circuit block is a small encapsulated unit containing a basic electronic circuit, designed to accept and operate upon a specific type of input signal and to produce a specific type of electrical output. A number of different blocks can be combined to form larger parts of an electronic digital system.

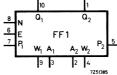

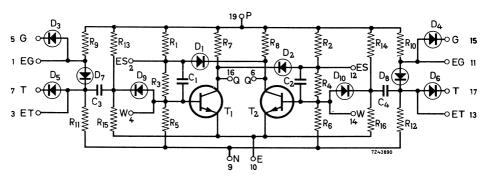

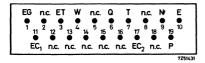

In this series the following units and assembled panels are available:

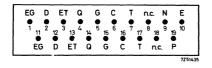

| description                  | colour | abbreviation | catalog number | page  |

|------------------------------|--------|--------------|----------------|-------|

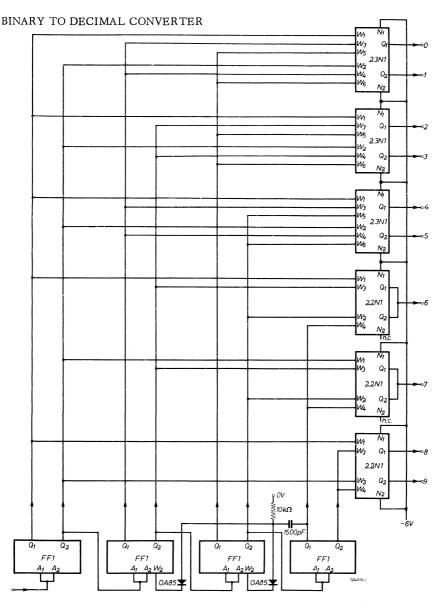

| Flip-flop                    | red    | FF1          | 2722 001 00001 | A57   |

| Flip-flop                    | red    | FF2          | 2722 001 00011 | A61   |

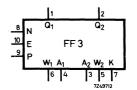

| Flip-flop                    | red    | FF3          | 2722 001 00021 | A65   |

| Flip-flop                    | red    | FF4          | 2722 001 00031 | A69   |

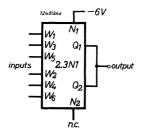

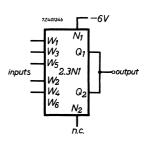

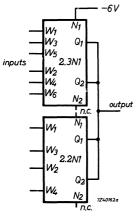

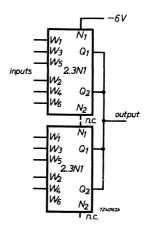

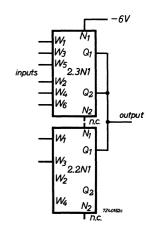

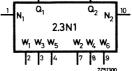

| Dual 3-input negative gate   | orange | 2.3N1        | 2722 001 01001 | A73   |

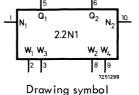

| Dual 2-input negative gate   | orange | 2.2N1        | 2722 001 01011 | A75   |

| Dual 3-input positive gate   | orange | 2.3P1        | 2722 001 02001 | A77   |

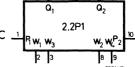

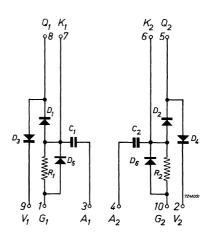

| Dual 2-input positive gate   | orange | 2.2P1        | 2722 001 02011 | A79   |

| Dual pulse logic             | orange | 2.PL1        | 2722 001 03001 | A81   |

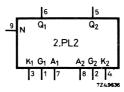

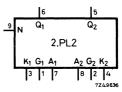

| Dual pulse logic             | orange | 2.PL2        | 2722 001 03011 | A85   |

| Emitter follower/inverter    |        |              |                |       |

| amplifier                    | yellow | EF1/IA1      | 2722 001 07001 | A89   |

| Dual emitter follower        | yellow | 2.EF1        | 2722 001 05001 | A91   |

| Dual inverter amplifier      | yellow | 2.IA1        | 2722 001 06001 | A95   |

| Dual emitter follower        | yellow | 2.EF2        | 2722 001 05011 | A99   |

| Dual inverter amplifier      | yellow | 2.IA2        | 2722 001 06011 | A103  |

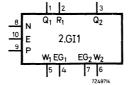

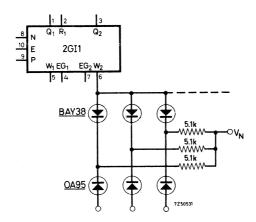

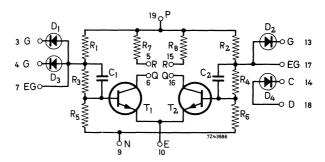

| Dual gate inverter           | yellow | 2.GI1        | 2722 001 08001 | B31   |

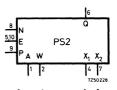

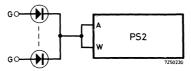

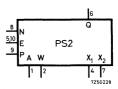

| Pulse shaper                 | green  | PS1          | 2722 001 11001 | A107  |

| Pulse shaper                 | green  | PS2          | 2722 001 11011 | A111  |

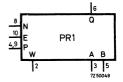

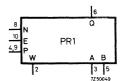

| Positive reset unit          | blue   | PR1          | 2722 001 22001 | A117  |

| One-shot multivibrator       | green  | OS1          | 2722 001 10001 | A121  |

| One-shot multivibrator       | green  | OS2          | 2722 001 10011 | A125  |

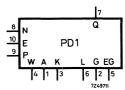

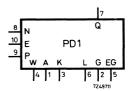

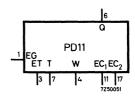

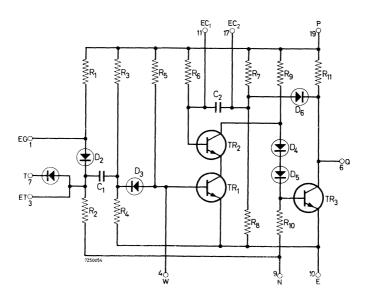

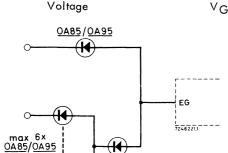

| Pulse driver                 | green  | PD1          | 2722 001 13011 | A131  |

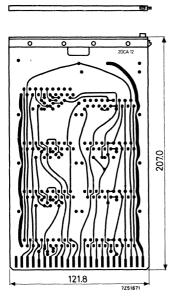

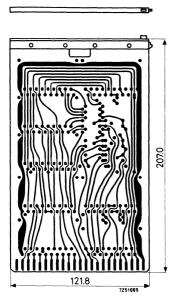

| Printed-wiring board for PD1 |        | PDA1         | 4322 026 34710 | A 181 |

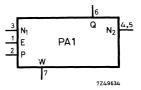

| Power amplifier              | -      | PA1          | 2722 032 00011 | A137  |

| Printed-wiring board for PA1 |        | PAA1         | 4322 026 33630 | A179  |

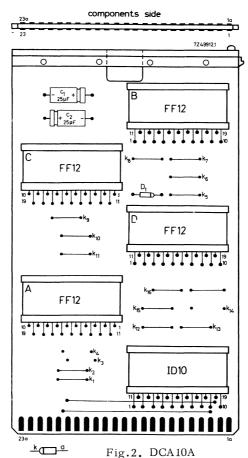

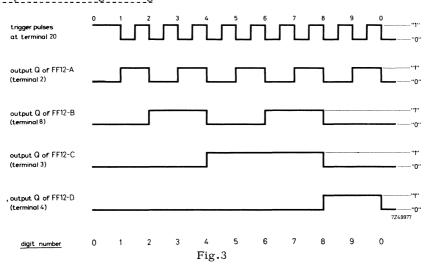

| Decade counter               | -      | DC1          | 2722 009 00001 | A141  |

| Dual decade counter          | -      | 2.DCA2       | 2722 009 00011 | A147  |

| Reversible counter           | -      | BCA1         | 2722 009 00021 | A153  |

| Decade counter and           |        |              |                |       |

| numerical indicator          |        |              |                |       |

| tube driver assembly         |        | DCA3         | 2722 009 00031 | A 159 |

| Dual numerical indicator     |        |              |                |       |

| tube driver assembly         |        | 2.ID1        | 2722 009 05001 | A167  |

A number of static input and output devices can be used in conjunction with  $100~\mathrm{kHz}$  circuit blocks, see chapter "INPUT/OUTPUT DEVICES"

For power supplies, printed-wiring boards, etc. see section "ACCESSORIES FOR CIRCUIT BLOCKS 100 kHz SERIES"

### ADVANTAGES OF CIRCUIT BLOCKS

Some of the outstanding advantages of circuit blocks are:

- saving of time and effort in the development and manufacture of electronic equipment;

- saving of handling, mounting and testing costs in manufacture;

- high and constant quality level;

- simplification of stock-keeping and ordering;

- rationalisation through standardised units.

### FIELDS OF APPLICATION

Circuit blocks can in general be used in all digital data-handling equipment, such as for:

- signalling;

- measuring and testing;

- computing;

- data handling;

- controlling;

- laboratory uses.

For detailed design and application information section "Some Practical Circuits", should be consulted.

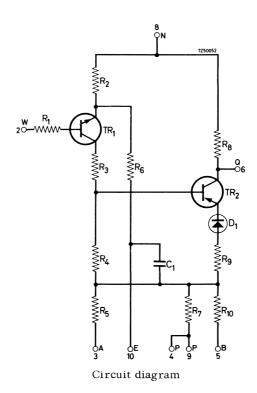

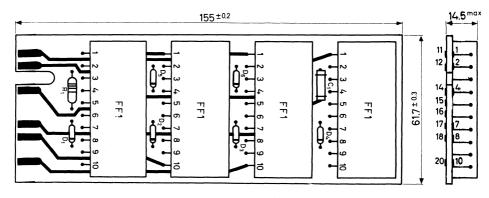

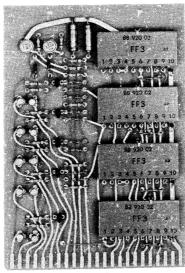

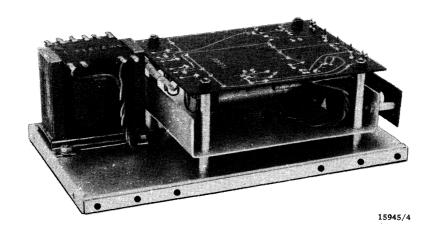

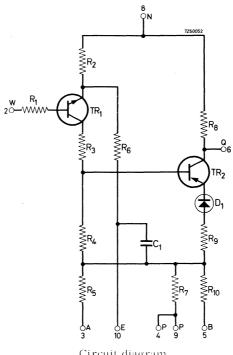

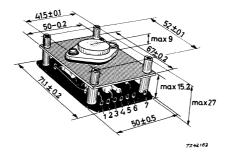

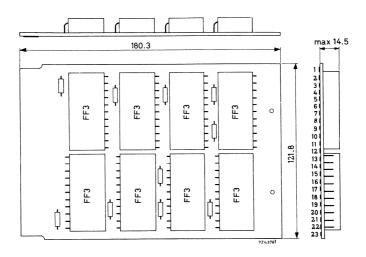

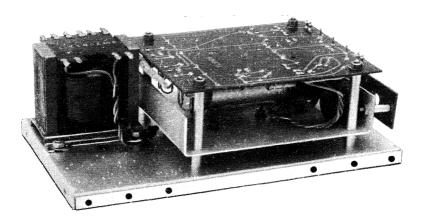

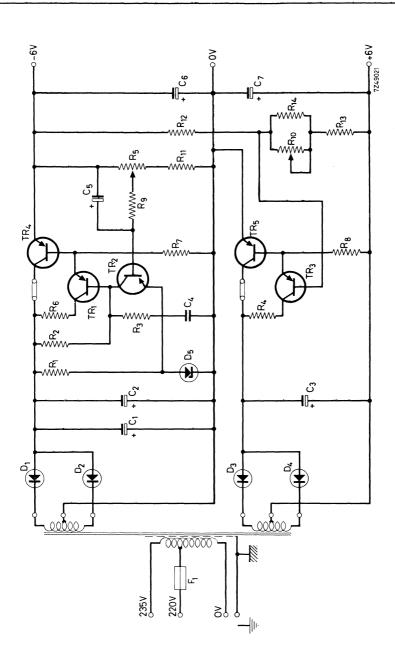

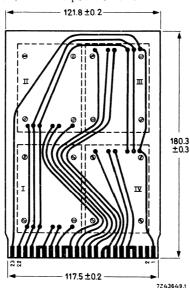

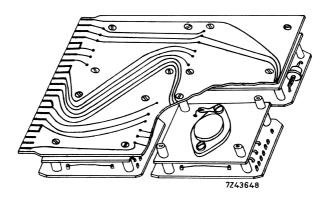

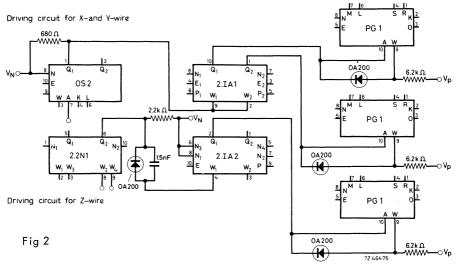

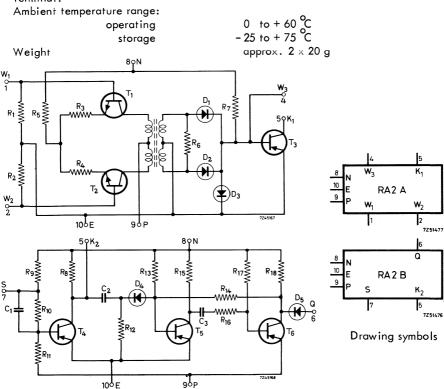

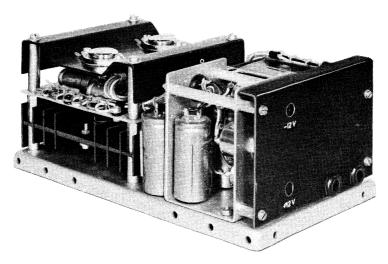

## CONSTRUCTION

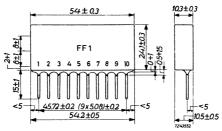

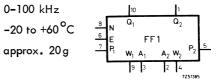

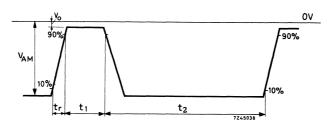

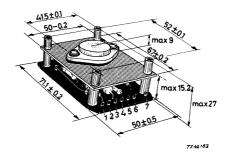

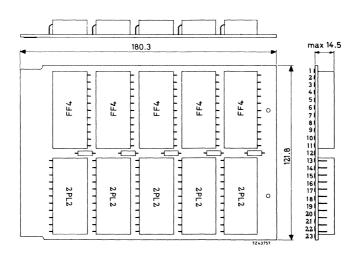

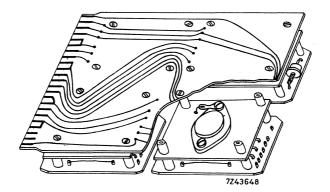

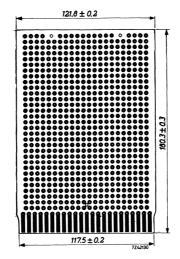

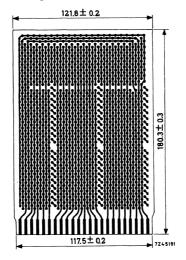

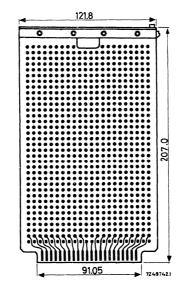

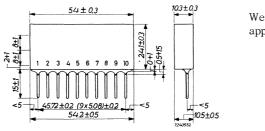

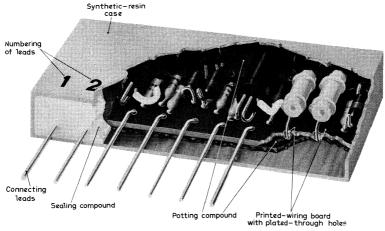

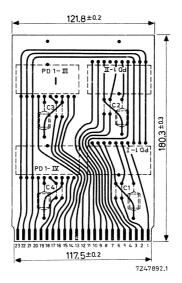

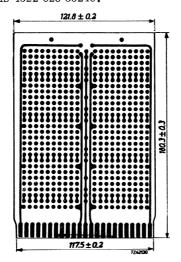

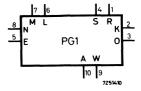

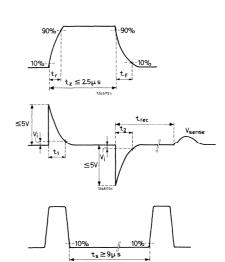

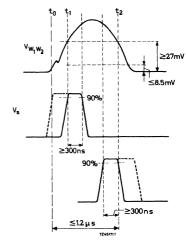

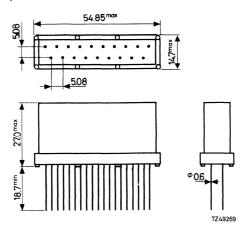

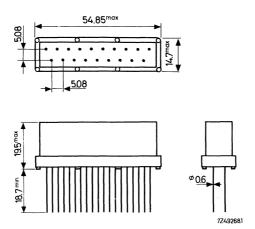

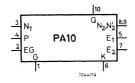

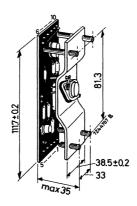

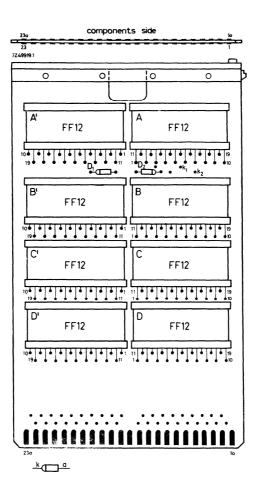

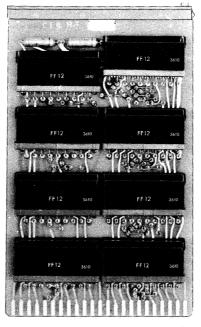

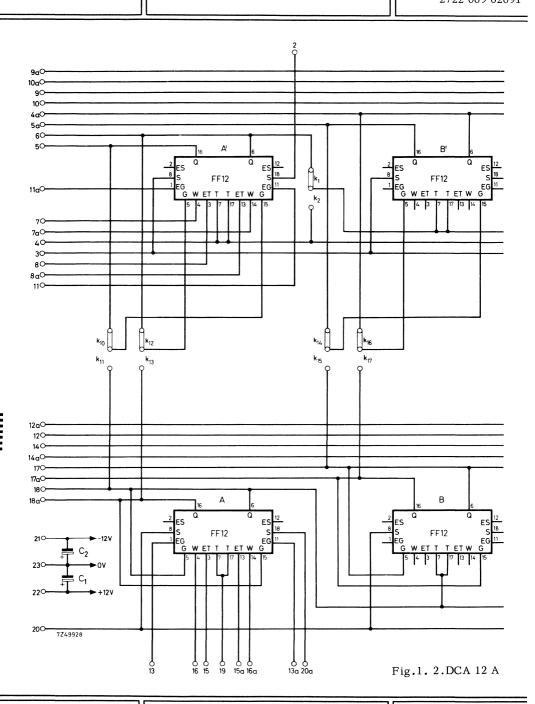

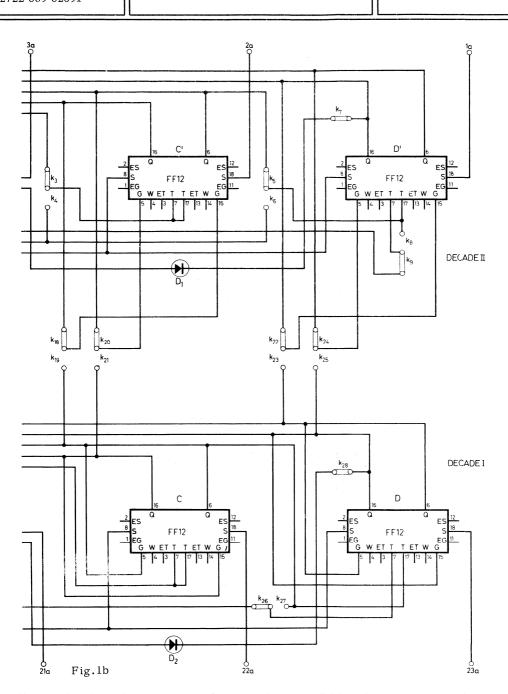

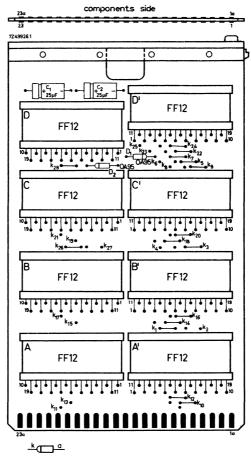

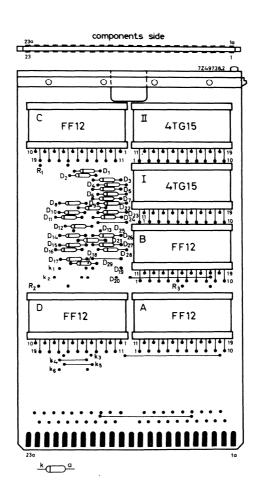

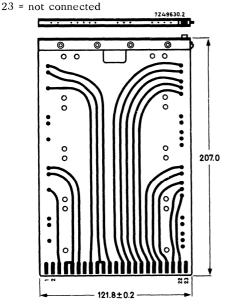

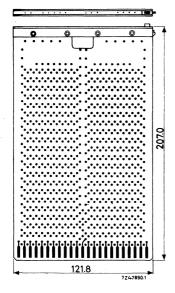

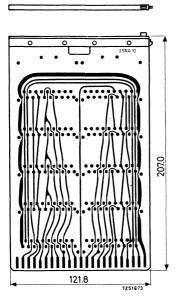

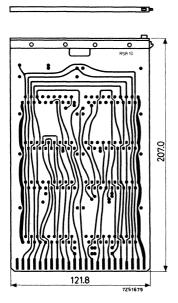

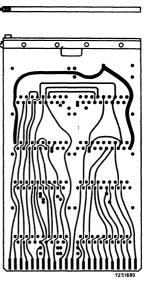

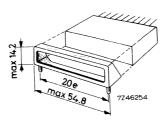

Fig. 1 Dimensional drawing of the circuit block

The dimensions of all 100 kHz circuit blocks are approximately 54 mm x 24 mm x 11 mm (see fig.1). Out of one side of 54 mm x 11 mm emerge ten wire terminals of 0.7 mm diameter and 15 mm length. The distances between the wires are 5.08 mm (0.2 in) in accordance with the I.E.C. standard hole grid for printed-wiring boards.

The blocks are colour-coded, a different colour being used for each group of functions.

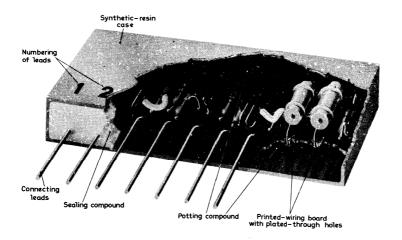

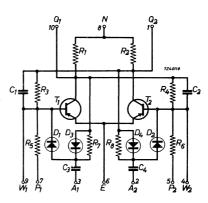

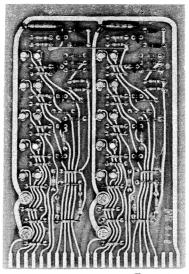

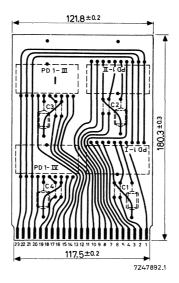

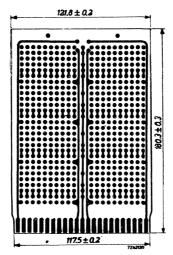

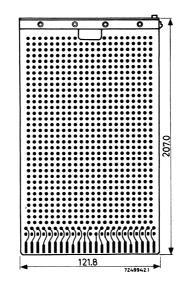

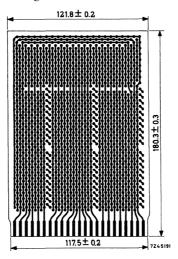

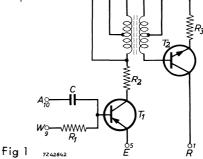

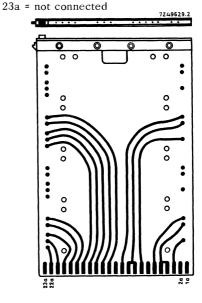

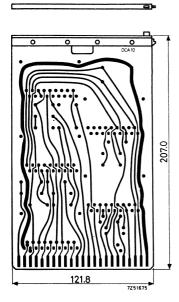

Fig. 2 Cut-away view of a circuit block

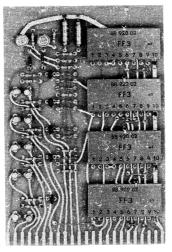

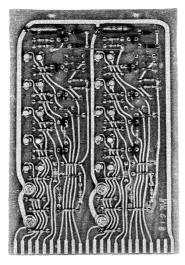

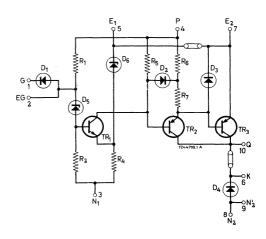

The construction of a  $100\ \text{kHz}$  circuit block can easily be seen in the cut-away view of Fig.2.

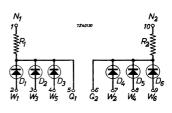

The electronic components, of which the circuit is made up (transistors, diodes, resistors, capacitors) are mounted on a printed-wiring board. This board is provided with plated-through holes to ensure reliable joints due to the large contact area of soldered contacts. The connecting leads are also mounted on the printed-wiring board.

Protection against mechanical shock and vibration is provided by the resilient potting compound, whilst atmospheric influences are excluded by the sealing compound, by which the synthetic resin case is hermetically closed.

For the sake of reference the connecting leads are numbered 1 to 10.

# DESIGN CONSIDERATIONS AND RELIABILITY

The main problem in the design of electronic equipment is to attain an optimum level of reliability. The effective functional reliability of an electronic apparatus is - once a given circuit has been determined - exclusively dependent on the stability of the characteristics of the circuit components during their lives.

Though the drift of the characteristics of the present-day components has already been brought down to a very low value, the circuit has to be designed so as to be capable of accepting the still remaining drift. This factor and the nominal spread in the component values determines the total spread to be reckoned with during life.

A very safe design can be achieved by adopting the so-called "worst-case design" principle, in which these total spreads in their most unfavourable combination are taken as a design basis. As far as systematic failures are concerned, these considerations lead to a very safe circuit.

Generally, the performance of a circuit, designed on this basis, is rather poor, however, because of the extreme tolerance combinations that have been taken into account. On the other side, the probability that these extreme combinations occur is practically nil, the probability of "survival" of the circuit element being completely dependent on sudden failures, which are mostly of a non-systematic and catastrophic nature.

The choice of the components in the circuit blocks, the provisions taken in the manufacture of these components, as well as the special protective measures lead to a strong reduction of such sudden failures. Furthermore, a very safe electronic design procedure is followed, applying all available knowledge on the specific statistic behaviour of the components. In this way units with a high standard of reliability, a long life and a high electronic performance are obtained.

It stands to reason that a good performance of the circuit blocks can only be guaranteed, if the user, in his turn, sticks to the operating conditions given by the manufacturer. These operating conditions and guarantee, which apply to all types of circuit block, are given below.

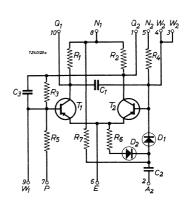

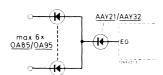

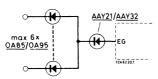

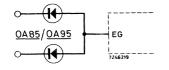

### CHARACTERISTICS

Besides passive network elements (resistors, capacitors), only semiconductor devices are incorporated in the circuit blocks, viz. transistors, Ge-diodes and Si-diodes. As a result the inherent advantages of these semiconductors are reflected in the properties of the circuit blocks, such as low supply voltages and small power dissipation.

April 1968 A7

# :

# DESIGN CONSIDERATIONS AND RELIABILITY

The standard supply voltage of the circuit blocks is  $+6\,V$  and/or  $-6\,V$ , so that no special measures with respect to insulation and protection need be taken.

The power dissipation of the blocks is so small (20 to 100 mW) that no special precautions are necessary with regard to cooling.

The 100 kHz circuit blocks are guaranteed to work properly at the maximum speed of operation under maximum load conditions as given in the Data sheets in the temperature range of -20 °C to +60 °C (-4 °F to +140 °F).

For storage the temperature limits of -25 °C and +75 °C must not be exceeded.

Though the circuit blocks function reliably at any combination of the margins given with respect to supply voltage and ambient temperature, the maximum operational safety margin and the maximum life can be expected by operating the units as closely as possible to the given nominal values of +6~V and -6~V for the supply voltages and 25  $^{\circ}$ C (77  $^{\circ}$ F) for the ambient temperature.

Apart from some output devices the circuit blocks are designed for an operational speed of  $100~\rm kHz$ . Because of the large safety margin that has already been taken into account, no further speed-derating is necessary.

# **TEST SPECIFICATIONS**

Before and during manufacture samples of circuit blocks are regularly subjected to the following tests.

- (1) Shock test and vibration test according to method 202A and 201A of MIL-STD-202, terminals tested on strength, tests on mounting, soldering, lacquer and coding.

- (2) corrosion test (salt haze), according to method 101A of MIL-STD-202 (condition B, 48 hours).

- (3) temperature cycling test, according to method 102A of MIL-STD-202 (5 cycles from -25  $^{\rm o}$ C to +65  $^{\rm o}$ C).

- (4) dip test, according to method 104A of MIL-STD-202 (2 cycles 65  $^{\rm O}{\rm C}/20$   $^{\rm O}{\rm C}$ , condition B, NaCl).

- (5) accelerated humidity test, according to method 106A of MIL-STD-202 (10 cycles 65 °C).

- (6) Long-term humidity test (units not operating), according to I.E.C.68, C IV (40 °C, relative humidity: 90% to 95%, duration longer than 2000 hours, functional marginal measurements after 250, 1000 etc. hours).

- (7) as item 6, but units operating under the most unfavourable electrical conditions.

- (8) long-term test at max. temperature (60 °C), units operating under the most unfavourable electrical conditions. Duration and measurements as item 6.

# THE DESIGN OF A CIRCUIT WITH CIRCUIT BLOCKS

### BLOCK DIAGRAM

The growing complexity of the electronic system of to-day calls for a simple logical unambiguous way of representation in the system circuit diagram. Effective use is made of a block diagram, in which each symbol represents a specific unit function, which may represent a system component of different complexity. Such a block in the diagram may denote, for instance, anything between a complete production plant and a small basic electronic function, such as a flip-flop, a gate circuit etc. The latter can be considered as basic subassemblies for electronic systems. The circuit blocks belong to this category, each type representing a single functional element or a combination of two of such elements.

### BASIC LOGIC SYMBOLS

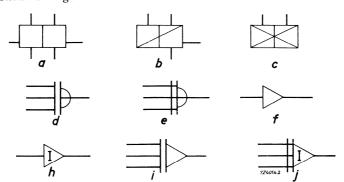

When a logic circuit is to be designed, whether it should be equipped with circuit blocks or any other elements, it may be useful to make up a block diagram without paying any attention to the technical set-up for the time being. In such a block diagram use can be made of symbols of purely functional elements, some of which are shown in Fig.3.

Fig.3. Symbols for logic circuits

- a. bi-stable multivibrator (flip-flop)

- b. mono-stable multivibrator (one-shot)

- c. a-stable multivibrator

- d. and-gate

- e. or-gate

- f. non-inverting amplifier (emitter-follower)

- h. inverter

- i. and-gate with emitter follower

- j. or-gate with inverter

# THE DESIGN OF A CIRCUIT WITH CIRCUIT BLOCKS

From the symbols in Fig.3 only the and-gate, the or-gate and the inverter perform a purely logic function. According to the Boolean algebra the relations between the output signal and the input signal of these elements are as follows:

AND-gate: (Fig.3d):  $P = A \cdot B \cdot C \cdot ... \cdot N$ OR-gate: (Fig.3e):  $P = A + B + C + ... \cdot + N$ Inverter (Fig.3h):  $P = \overline{A}$  ( $\overline{A} = "NOT A"$ )

A, B, C etc. can attain the values "0" (no signal) and "1" (signal). It should be remembered, that in terms of Boolean algebra 1+1=1, so that the value of Pin the OR-gate can never exceed 1. The action of the inverter is such, that an input signal "0" produces an output signal "1", or the reverse  $(\overline{0}=1, \overline{1}=0)$ .

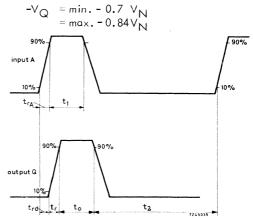

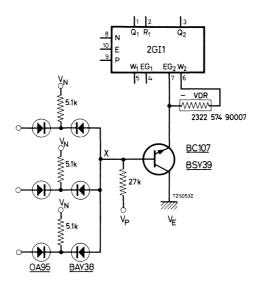

#### VOLTAGE LEVELS AND SIGNAL VALUES

In a binary system two discrete states can be distinguished, to which the logical values "0" and "1" are assigned. In electronic circuits these values are commonly allocated to the output voltage(s) of a flip-flop, which, in the case of circuit blocks, are approximately 0 V and 0.7  $V_N$  or more negative ( $V_N$  being the negative supply voltage).

Since it is immaterial, whether one of these voltage levels is indicated by "0" or "1", or vice versa, they are denoted by "negative low" (approx. 0 V) and "negative high" (0.7  $V_N$  or more negative).

#### COMBINATION OF LOGIC SYMBOLS

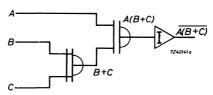

When Boolean functions of a more complex character than those of the AND-gate, the OR-gate or the inverter are dealt with, combinations of these elements must be used. As an example the function  $P = \overline{A \cdot (B+C)}$  will be considered. This function is performed by the following logic circuit (Fig. 4).

Fig. 4. Logic circuit for obtaining the function  $P = \overline{A \cdot (B + C)}$ .

In some cases, and specially when a particular arrangement cannot be used for technical reasons, another arrangement can be found by converting the function into an equivalent function, whereby the rules of Boolean algebra may come in useful. The function  $P = \overline{A} \cdot (B + \overline{C})$  can be converted into the function  $P = \overline{A} + \overline{B} \cdot \overline{C}$ , which corresponds to the logic circuit of Fig.5. From the table below, in which all combinations of A, B and C are considered, it can easily be seen that the functions  $P = \overline{A} \cdot (B + \overline{C})$  and  $P = \overline{A} + \overline{B} \cdot \overline{C}$  are equivalent.

Fig.5. Logic circuit for obtaining the function  $P = \overline{A} + \overline{B} \cdot \overline{C}$ .

### Table

| A | В | С | Ā | B | C | B + C | $\overline{B}$ . $\overline{C}$ | A(B + C) | $\overline{A(B+C)}$ | $\overline{A} + \overline{B} \cdot \overline{C}$ |

|---|---|---|---|---|---|-------|---------------------------------|----------|---------------------|--------------------------------------------------|

| 0 | 0 | 0 | 1 | 1 | 1 | 0     | 1                               | 0        | 1                   | 1                                                |

| 1 | 0 | 0 | 0 | 1 | 1 | 0     | 1                               | 0        | 1                   | 1                                                |

| 0 | 1 | 0 | 1 | 0 | 1 | 1     | 0                               | 0        | 1                   | 1                                                |

| 0 | 0 | 1 | 1 | 1 | 0 | 1     | 0                               | 0        | 1                   | 1                                                |

| 1 | 1 | 0 | 0 | 0 | 1 | 1     | 0                               | 1        | 0                   | 0                                                |

| 0 | 1 | 1 | 1 | 0 | 0 | 1     | 0                               | 0        | 1                   | 1                                                |

| 1 | 0 | 1 | 0 | 1 | 0 | - 1   | . 0                             | 1        | 0                   | 0                                                |

| 1 | 1 | 1 | 0 | 0 | 0 | 1     | 0                               | 1        | 0                   | 0                                                |

### RULES OF BOOLEAN ALGEBRA

The equations given below can be used advantageously to simplify and convert logic functions. They can easily be verified by making up tables as shown above.

| A + 0 = A                                                                |                                                                                   | A = 0 = 0                                                                                       |

|--------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| A + 1 = 1                                                                |                                                                                   | A . 1 = A                                                                                       |

| A + A = A                                                                |                                                                                   | $A \cdot A = A$                                                                                 |

| $A + \overline{A} = 1$                                                   |                                                                                   | $A \cdot \overline{A} = 0$                                                                      |

| $A + A \cdot B = A$                                                      |                                                                                   | $A \cdot (A + B) = A$                                                                           |

| $A + \overline{A} \cdot B = A + B$                                       |                                                                                   | $A \cdot (\overline{A} + B) = A \cdot B$                                                        |

| $A \cdot (B + C) = A \cdot B + A \cdot C$                                |                                                                                   | $(A + B) \cdot (A + C) = A + B \cdot C$                                                         |

| $(A + B) \cdot (C + D) = \overline{A \cdot \overline{B} + \overline{C}}$ | . <u>D</u>                                                                        | $(A \cdot B) + (C \cdot D) = (\overline{A} + \overline{B}) \cdot (\overline{C} + \overline{D})$ |

| $A + B + C + \dots$                                                      | $+ N = \overline{\overline{A} \cdot \overline{B} \cdot \overline{C} \cdot \dots}$ |                                                                                                 |

| A . B . C                                                                | $N = \overline{\overline{A} + \overline{B} + \overline{C}}$                       | $\overline{N}$                                                                                  |

| $\overline{A} + \overline{B} + \overline{C} + \dots$                     | $+ \overline{N} = \overline{A \cdot B \cdot C \cdot \dots}$                       | N                                                                                               |

| $\overline{A} \cdot \overline{B} \cdot \overline{C} \cdot \dots$         | $\overline{N} = \overline{A+B+C}$                                                 | + N                                                                                             |

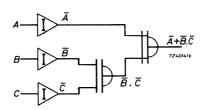

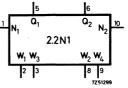

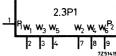

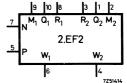

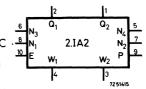

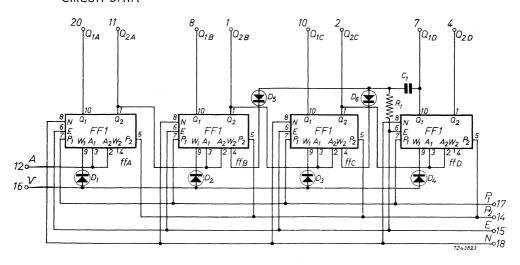

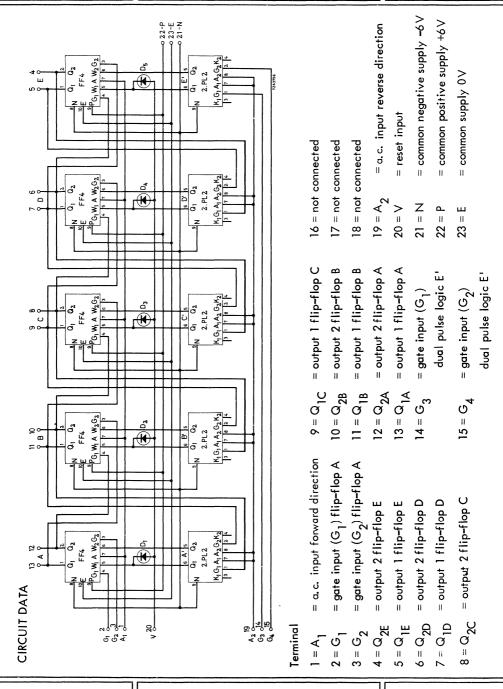

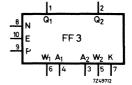

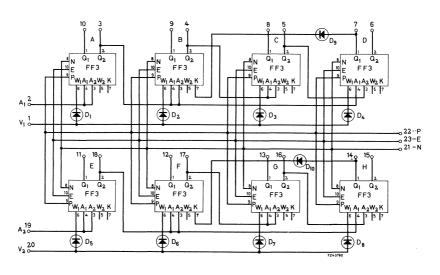

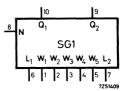

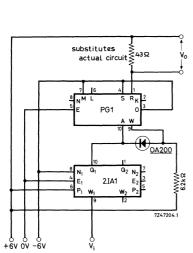

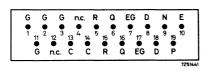

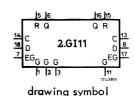

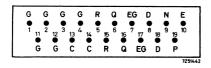

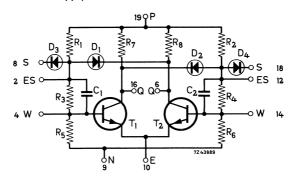

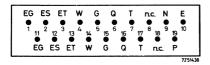

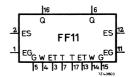

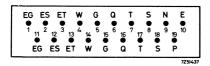

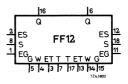

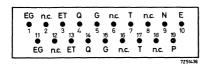

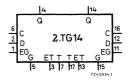

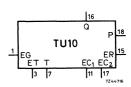

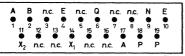

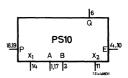

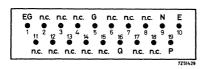

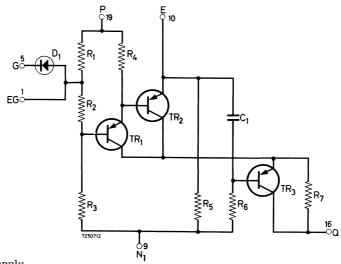

### SYMBOLS FOR CIRCUIT BLOCKS

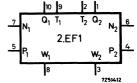

After the block diagram with logic symbols has been made up, the logic symbols should be translated into circuit blocks. To this end a wiring diagram is made in which the logic symbols are replaced by symbols representing the corresponding circuit blocks. The latter symbols, recommended for this purpose, are given in the Data Sheets of the circuit blocks. Each of these symbols consists of a rectangle, in which the type of circuit block and the connections are indicated (Fig.6). Since also the reference numbers of the connecting leads are indicated in the symbol, the equipment can be constructed directly from the circuit block diagram.

Fig.6. Typical symbol of a circuit block (FF1).

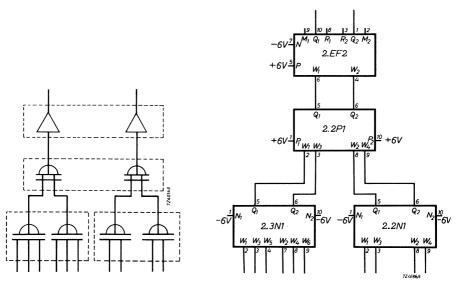

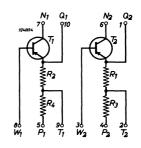

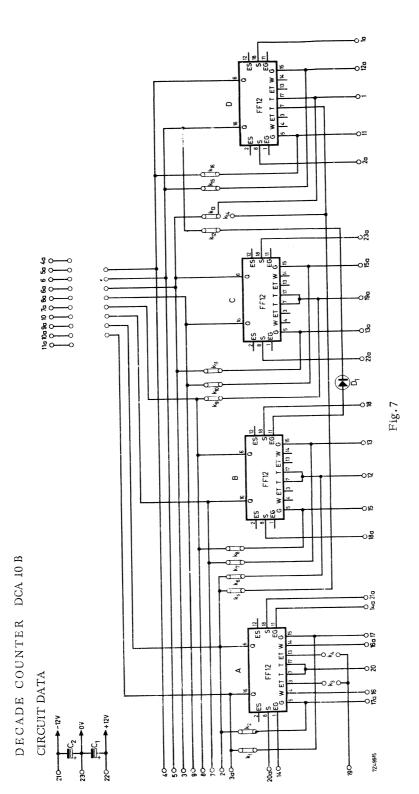

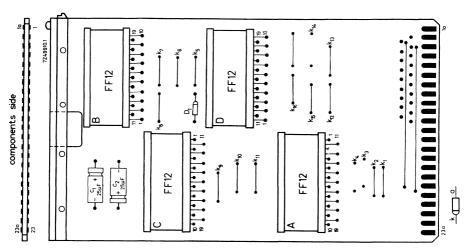

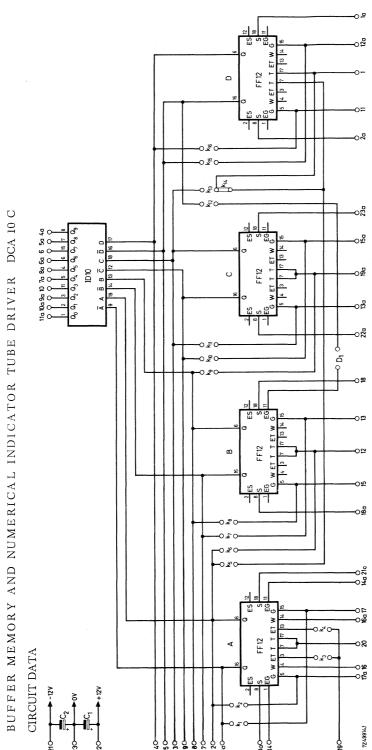

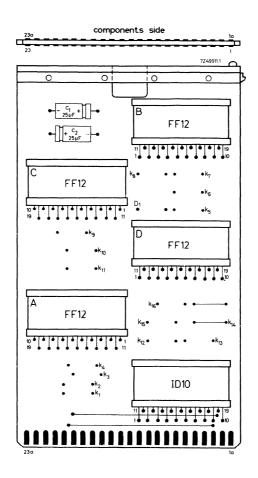

In Fig.7 an example is given of how logic symbols can be combined so as to obtain an arrangement that can be built up from circuit blocks. In this figure the convention "negative low" = "0" and "negative high" = "1" has been adopted, which involves, that the AND-operation is performed by an N-gate and the OR-operation by a P-gate (see under "Gates" in section "Operational Notes").

Fig.7. Translation of logic functional symbols into circuit block symbols.

A15

# THE DESIGN OF A CIRCUIT WITH CIRCUIT BLOCKS

#### THE LOADING TABLE

Since the loadability of circuit blocks is limited, they may not be arranged arbitrarily. A circuit block diagram, made up from a diagram with logic symbols, should be carefully checked on the basis of the Loading Table.

From this table the number of units that can be driven by any other unit can be taken. When a unit has output terminals with different loadability these data are given separately.

It may be noted that the Loading Table is made up for combinations of units under supply voltage tolerances of  $\pm$  5%, whilst part of the earlier types of blocks (see data sheets) allow for a supply voltage tolerance of  $\pm$  10%.

The gain in performance obtained at those reduced tolerances has been taken into account in the table. In those cases where a proper functioning is assured a pulse rise time of  $0.7\,\mu s$  has also been calculated with, though  $0.4\,\mu s$  has been prescribed earlier. The result is an overall improvement in loadability in the Loading Table compared with earlier publications.

In the case of amplifier units, the output data are dependent on the input driving signal; for these units the loadability is given for different preceding units or preceding chain of units.

The EF 2 is especially suited to drive a common-emitter stage; for this combination the loadability is also given.

The number of negative gates (N 1) which can be driven by any other unit at a "negative low" output level, depends, due to diode leakage current, on the number of other gate inputs which are at a "negative high" level. In this Loading Table the assumption is made that three other inputs of each driven gate are at a "negative high" level.

If not indicated separately in the Loading Table all N and P terminals of each unit are connected to  $V_{\rm N}$  respectively Vp.

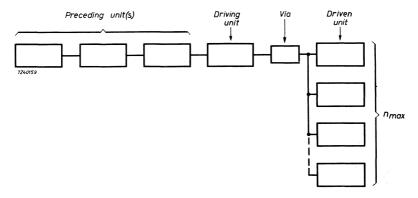

The general set-up of the Loading Table is elucidated in the diagram given below.

Fig.8. Diagram to explain the Loading Table.

# 100 kHz Series

# THE DESIGN OF A CIRCUIT WITH CIRCUIT BLOCKS

GENERAL

If a specific combination of circuit blocks appears to be inadmissible, it should be rearranged into a permissible combination. Boolean algebra can be used for this purpose.

In some cases a loading, differing slightly from that given in the Loading Table, may be possible.

In this case it must be carefully checked, whether the input signal requirements of the driven units do not exceed the given corresponding output data of the driving unit. It also should be considered that the limiting values of the input signals of the driven unit are never exceeded.

This concerns the values of voltage levels, currents and switching times, which can be derived from the data sheets.

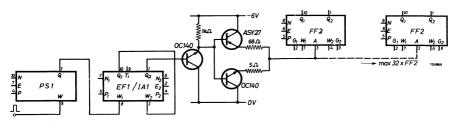

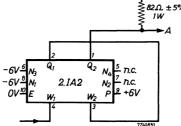

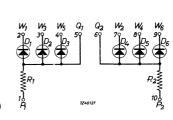

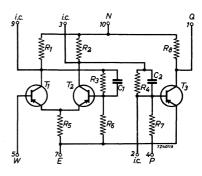

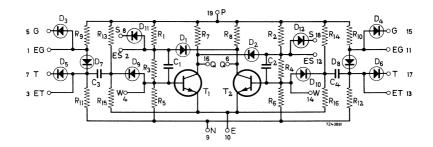

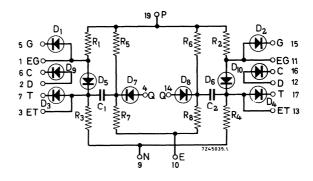

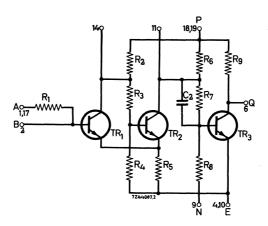

# SOME PRACTICAL CIRCUITS

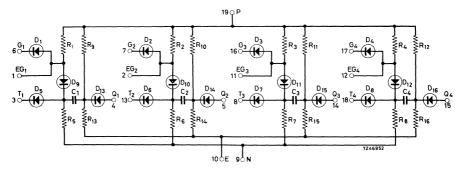

In this section some practical examples are given for the application of  $100~\rm kHz$  circuit blocks. Since most circuit blocks comprise twin units or two separate functional units in certain cases only half the symbol is given.

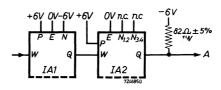

For the sake of simplicity the supply lines are not drawn in many of the figures given below. Normally the N terminals are connected to the -6 V supply, the P terminals to the +6 V supply and the E terminals to earth (common to both supply voltages). If a supply terminal should not be connected to the corresponding supply line this is indicated by "n.c." (not connected).

In the applications given the following convention is adopted:

```

"negative low" = binary "0"

"negative high" = binary "1".

```

According to this convention a Negative gate (2.3N1 or 2.2N1) is employed to perform the logical AND operation and a Positive gate (2.3P1 or 2.2P1) to perform the logical OR operation (see Operational Notes).

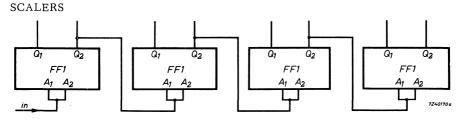

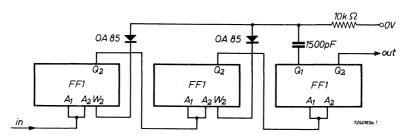

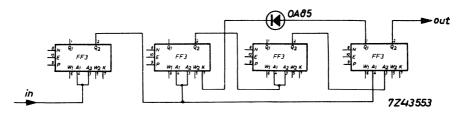

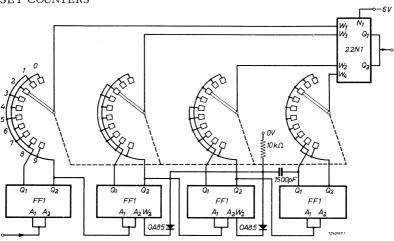

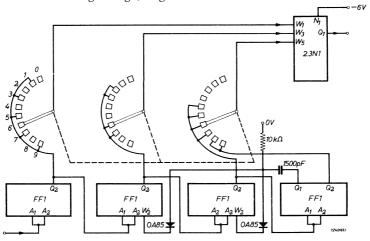

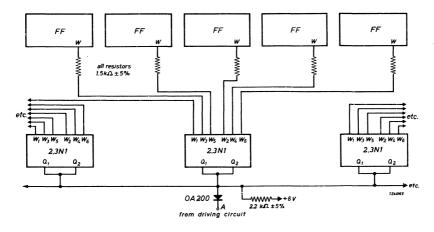

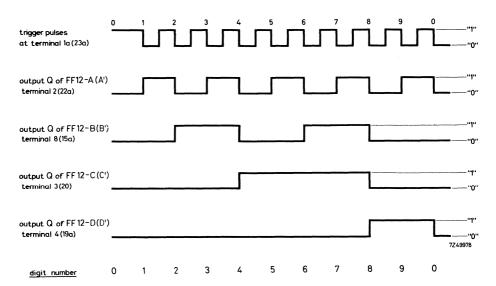

Fig. 9. Scaler of 16 (Binary counter with 4 flip-flops)

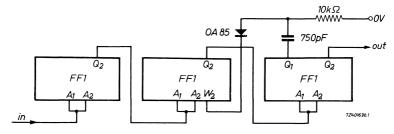

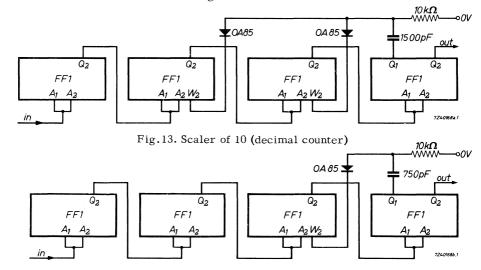

Below some scalers are given in which pulse feed-back is applied to obtain a dividend that is not a power of 2.

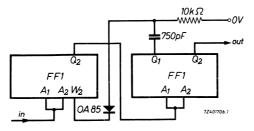

Fig.10. Scaler of 3

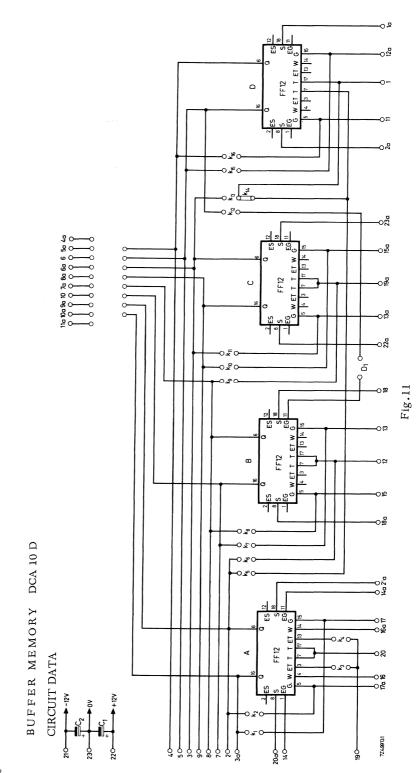

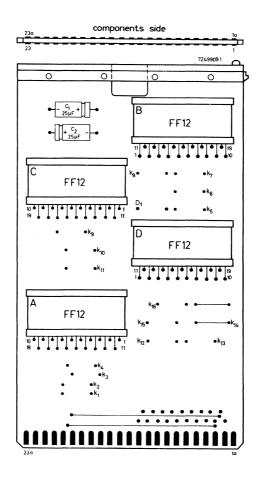

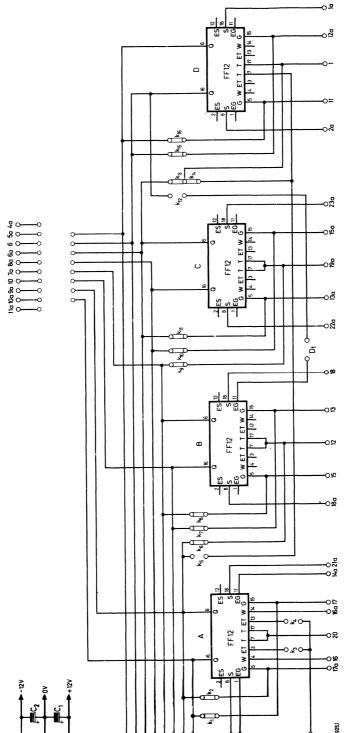

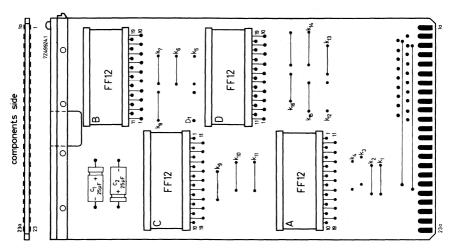

Fig.11. Scaler of 5

Fig.12. Scaler of 6

Fig.14. Scaler of 12

Apart from the above mentioned pulse feedback principle also an intermediate gate can be used to skip a number of positions in order to attain scalers of dividends that are no powers of 2. The advantages of this type of circuit is that spurious pulses, as occurring at the output of the scaler with pulse feedback, are avoided. An example of a decimal counter designed on this principle is given below.

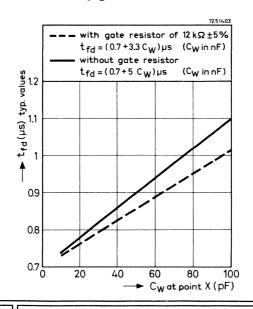

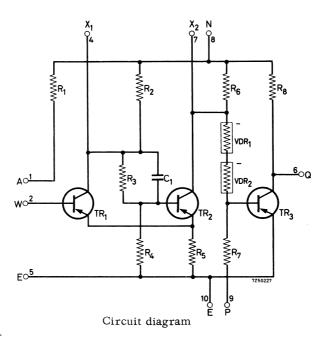

Fig.15. Decimal counter, maximum speed 60 kHz

For a speed of 100 kHz the resistor in the 2Nl block must be shunted externally by a  $12~\rm k\Omega \pm 5\%$  resistor or the 2Nl must be replaced by a circuit block 2.IAl, connected to perform the same gate function.

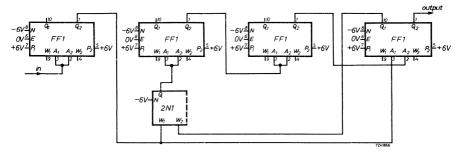

Fig.16. Decimal counter, maximum speed 100 kHz

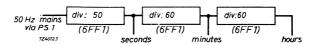

Fig.17. Time code frequency divider

### MULTIPLE INPUT GATES

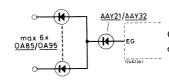

Fig.18. 6-input N-gate composed of one 2.3N1

Fig.19. 5-input N-gate composed of one 2.3Nl

Fig.20. 10-input N-gate composed of one 2.3N1 and one 2.2N1

Fig.21. 11-input N-gate composed of two 2.3N1's

Fig.22. 8-input N-gate composed of one 2.3N1 and half a 2.2N1.

A20

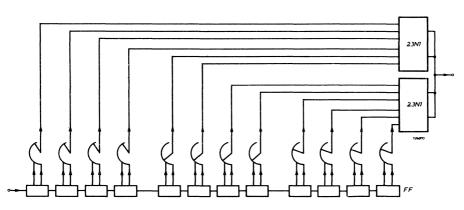

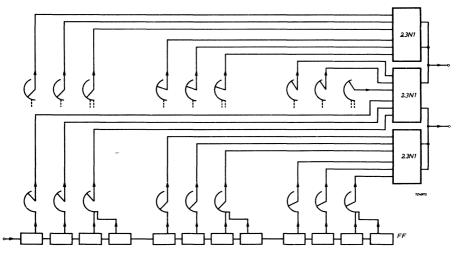

Fig.23. A count of n in the decimal counter produces a "1" signal at the output n at the right. All N, E and P terminals of the flip-flops should be connected to the corresponding supply lines.

### PRESET COUNTERS

Fig.24. General purpose circuit. An output voltage is produced when the decimal counter stores the number chosen by means of the 10-position 4-wafer switch. The circuit may also be used for the determination of a time interval by counting cycles of an alternating voltage, e.g. the mains.

Fig.25. Simplified circuit for special applications. An output signal is produced when the decimal counter has reached the number chosen by means of the 10-position 3-wafer switch. When this number is exceeded the output signal may stay or recur. This phenomenon makes the circuit only useful for those applications in which these spurious signals do not interfere.

A22 April 1968

Fig.26. When the counter consists of several decades, it may be preselected by as many 10-position switches. The gates are combined to one gate. The circuit may also be of the 3-wafer switch type, as shown in Fig.19.

Fig.27. Preset counter with multiple programmes. More than one set of switches and gates may be connected to the same counter. Every output gives a signal when the counter has reached the number set by its associated switches. The switches may be of the 3 or 4-wafer type.

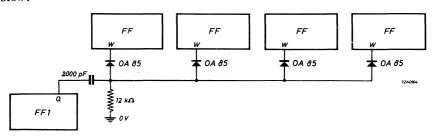

### SHIFT REGISTERS

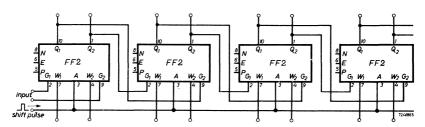

Fig.28. Shift register

Binary information, applied to the input terminals in complementary form, is shifted bit after bit into the register by means of the shift pulse. Set or Reset signals can be applied in parallel to the corresponding W terminals in the usual way (see Set and Reset circuits).

The outputs of the last FF2 can be connected crosswise to the gate inputs of the first ( $Q_1$  to  $G_2$  and  $Q_2$  to  $G_1$ ). A given information stored in the register will now circulate through it by means of the clock pulse.

By connecting the outputs of the last FF2 directly to the gate inputs of the first  $(Q_1 \text{ to } G_1 \text{ and } Q_2 \text{ to } G_2)$  scalers can be made which can very easily be decoded and preset; with 5 FF2's, e.g. a decimal counter can be made.

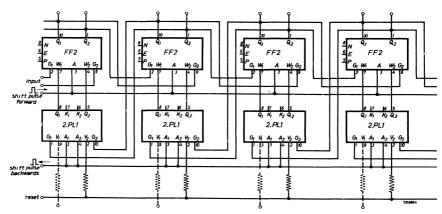

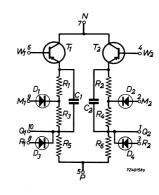

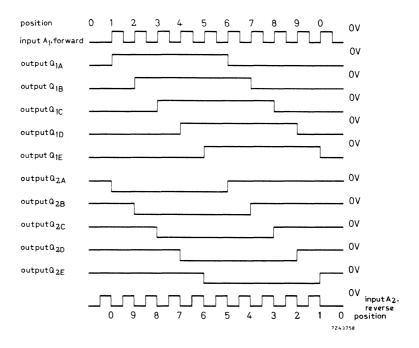

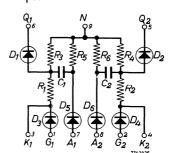

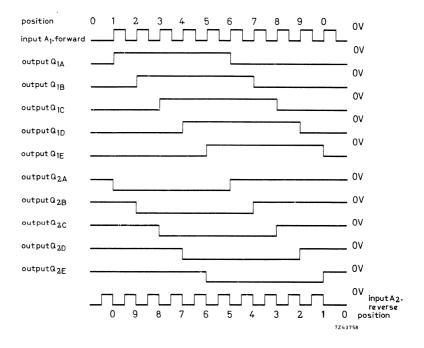

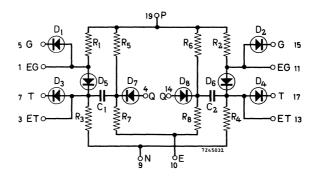

Fig.29. Bi-directional shift register

The circuit of Fig.28 can easily be converted into a bi-directional shift register by adding additional input pulse gates as incorporated in the unit 2.PL1. The information in the register can be shifted in both directions dependent on the input to which the shift pulse is applied. In the same way bi-directional decimal counters can be made according to the principle as indicated above.

The diodes, incorporated in the 2.PL1 (inputs  $\text{V}_1$  and  $\text{V}_2\text{)}$  can be used for negative Set or Reset signals.

### DRIVE CIRCUITS FOR SHIFT REGISTERS

Fig.30

Fig.31

Fig.32

### SET AND RESET CIRCUITS

A system in which flip-flops are used, often requires a means for setting or resetting. This can be realised as indicated in the figures below.

Fig.33

Input signal for resetting:

"0" (negative low)

Driving unit:

FF1, FF2, IA1, IA2, PS1 or OS1

Maximum number of flip-flops: 1

Fig.34

Input signal for resetting:

"1" (negative high)

Driving unit:

N-gate or N-P gate sequence

Maximum number of flip-flops: 1

A simple circuit for resetting flip-flops by a flip-flop FF1 is given in the figure below.

Fig.35

Resetting takes place on a positive voltage step at the Q terminal of the drving flip-flop.

When a large number of flip-flops has to be controlled, the following arrangement can be used.

Fig.36

The circuit of Fig. 36 can be driven by one of the circuits given below.

Fig.37

| Input signal for resetting:                   | "0" (negative low)             |         |                                                     |  |  |

|-----------------------------------------------|--------------------------------|---------|-----------------------------------------------------|--|--|

| Driving unit                                  | FF1, FF2, IA1, IA2, PS1 or OS1 | N1      | N1 -P1                                              |  |  |

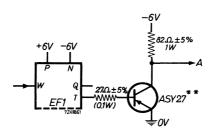

| Value of resistor $R_1$ in $\Omega$ +5 % 1)   | 82                             | 150/82) | 330 (200)                                           |  |  |

| $\pm 3 \%$ 1)<br>Max. number of flip-flops 1) | 32                             | 15 (32) | 330 <b>(</b> 200 <b>)</b><br>5 <b>(</b> 10 <b>)</b> |  |  |

<sup>1)</sup> The values between brackets apply to the circuit without the anti-bottoming connection (EF2-M terminal to collector ASY27). Consequently this circuit is for low speed operation only.

<sup>\*\*)</sup> See Fig.45.

Fig.38. (Low speed operation only)

Input signal for resetting:

"0" (negative low)

Driving unit:

FF1, FF2, IA1, IA2, OS1 or PS1

Maximum number of flip-flops: 32

Fig.39

Input signal for resetting:

"1" (negative high)

Driving unit: FF1, FF2, IA1, IA2, OS1 or PS1 Maximum number of flip-flops: 32

Fig.40

Input signal for resetting:

"1" (negative high)

Driving unit:

N1, N1-P1, IA1, IA2 or PS1

Maximum number of flip-flops: 3

\*\*) See Fig. 45

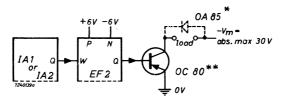

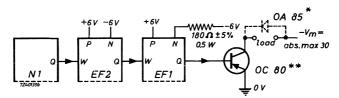

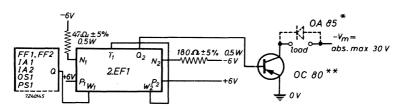

#### AMPLIFIER CIRCUITS FOR GATE SIGNALS

Fig.41. Iload = max. 5.5 mA

Fig. 42.  $I_{load} = max. 5.5 mA$

Fig. 43. Iload = max. 13 (29) mA  $^{1}$ )

Fig. 44. Iload = max. 35 (50) mA  $^{1}$ )

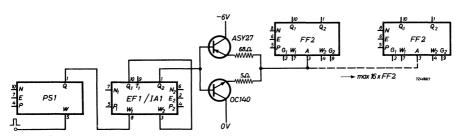

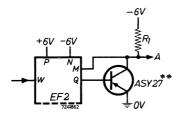

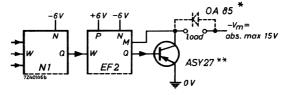

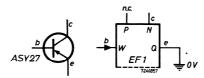

Fig.45. In the circuits given the transistor ASY27 can be replaced by the EF1 circuit.

<sup>1)</sup> The values between brackets apply to the circuit without the anti-bottoming connection (EF2-M terminal to collector ASY27). Consequently this circuit is for low speed operation only.

<sup>\*)</sup> In case of inductive load.

<sup>\*\*)</sup> See Fig.45.

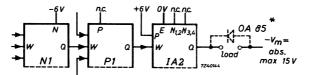

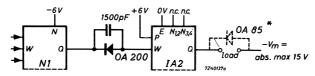

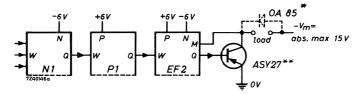

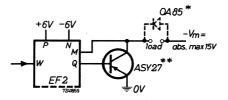

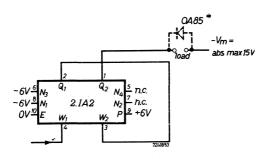

#### AMPLIFIER CIRCUITS

Fig.46

Driving circuit: FF1, FF2, IA1, IA2, OS1 or PS1 max. 70 (85) mA 1)

I<sub>load</sub>:

Fig.47

Driving circuit: FF1, FF2, IA1, IA2, OS1 or PS1

Iload:

max. 85 mA

Fig.48

Driving circuit: FF1, FF2, IA1, IA2, OS1 or PS1

Iload:

max. 85 mA

<sup>1)</sup> The values between brackets apply to the circuit without the anti-bottoming connection (EF2-M terminal to collector ASY27). Consequently this circuit is for low speed operation only).

<sup>\*)</sup> In case of inductive load.

<sup>\*\*)</sup> See Fig.45.

Fig.49

Driving circuit: N1, N1-P1, IA1, IA2, PS1

Iload: max. 70 mA

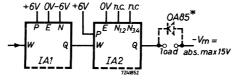

#### POWER AMPLIFIER CIRCUITS

Fig.50. Iload = max. 250 mA

Fig.51.  $I_{load} = max. 300 \text{ mA}$

<sup>\*)</sup> In case of inductive load

<sup>\*\*)</sup> The transistors have to be mounted on a heatsink (see relevant transistor data).

Fig.52.  $I_{load} = max. 300 \text{ mA}$

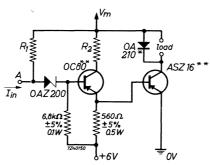

Fig.53

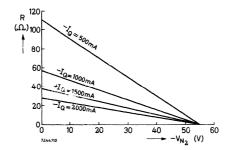

| Voltage         | -V <sub>m</sub>   | $12 \text{ V} \pm 15 \%$     | 1 24 V ±15 %                                 |

|-----------------|-------------------|------------------------------|----------------------------------------------|

| Resistors       | R <sub>1</sub>    | $470 \Omega \pm 5\%$ , 1 W   | $2.4 \text{ k}\Omega \pm 5\%, 0.5 \text{ W}$ |

|                 | R <sub>2</sub>    | $68 \Omega \pm 5 \%$ , $5 W$ | $150 \Omega \pm 5 \%$ , 10 W                 |

| Input current   | -I <sub>in</sub>  | min. 35 mA                   | min. 13.5 mA                                 |

| Load current    | I <sub>load</sub> | max. 2.6 A                   | max. 2.6 A                                   |

| Driving circuit | s                 | Fig.44 to 49                 | Fig.43 to 49                                 |

If there is a preference to use an output transistor ASZ17 or ASZ18 instead of the ASZ16, the stated maximum load current  $\rm I_{1oad}$  has to be multiplied by 0.6.

<sup>\*)</sup> To be used in case of inductive load.

<sup>\*\*)</sup> The transistors have to be mounted on a heatsink (see relevant transistor data).

#### SOME PRACTICAL CIRCUITS

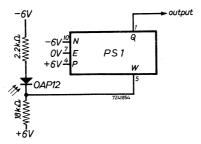

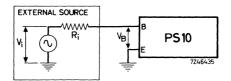

#### PHOTO-ELECTRIC PICK-UPS

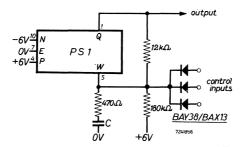

With a circuit block PS1 very simple photo-electric pick-ups can be made. For the output data of the circuits given below see the PS1 data sheet.

Fig.54

Switching level:

min. 13000 Lux (this lighting level can be achieved with a lens-end incandescent lamp of 2.2 V; 0.25 A)

Max. ambient temperature:

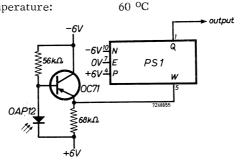

Fig.55

Switching level:

min. 3000 Lux (this lighting level can be achieved with a lens-end incandescent lamp of 2.2 V; 0.25 A)

Max. ambient temperature:

60 °C (only if the OAP12 and OC71 have been matched for proper leakage current compensation).

April 1968 A33

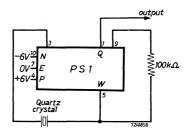

#### OSCILLATOR CIRCUITS

With a circuit block PS1 it is possible to make square wave oscillator circuits as given in the figures below.

Fig.56. Crystal controlled oscillator circuit. For the output data of this circuit see the PS1 data sheet.

Fig.57. Relaxation oscillator circuit. The oscillator may be controlled by more control signals as indicated in the figure. A "0" (negative low) level on one of these inputs stops the oscillator.

For a capacitor value C = 2500 pF f = approx. 100 kHz  $C = 250 \mu\text{F}$  f = approx. 1 Hz

Output data:

Voltage  $-v_{O}$ 0.2 max. Output level "negative low"  $-I_Q$ 1.2 Load current max. mA  $-v_{O}$ Voltage max. -0.7 $V_N$ Output level "negative high" Load current  $I_{O}$ 0.3 max. mA

For further data see PS1 data sheet.

April 1968

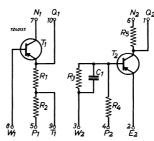

## **OPERATIONAL NOTES**

This chapter contains some general and specific remarks on the application of circuit blocks.

FLIP-FLOP

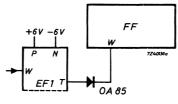

#### D.C. input signal

The flip-flops FF1, FF2, FF3 and FF4 can be set or reset on the W terminals by a negative or positive d.c. level. Attention should be paid to the W inputs being directly connected to the transistor base. When driven by a low-impedance source (e.g. the direct output of an emitter-follower or the negative power supply line) the transistor may be seriously overdriven and hence destroyed. The maximum permissible input current should therefore never be exceeded.

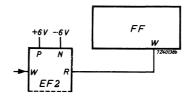

If the memory property of the flip-flop has to be maintained, the driving source should have a one-way action on the flip-flop; the source should therefore be connected to the W terminal by means of a series diode (see p. A26: SET AND RESET CIRCUITS). In order to attain a correct cut-off voltage level for this diode, the emitter-follower units EF1 and EF2, which can be used as driving sources for the flip-flop, are provided with a tapped output. The voltage level on the tap has the required value if the emitter-follower is driven by a "0" (negative low) signal.

The EF2 circuit block comprises the series diode (M<sub>1</sub> and M<sub>2</sub> output terminals).

#### Cascading of flip-flops

With n cascaded flip-flops FF1 or FF3 it is possible to construct frequency dividers with a dividend of  $2^n$ . When such a chain of flip-flops is used for counting, the total counting capacity amounts to  $2^n$  as well.

By using a pulse feedback or gating principle it is possible to skip a given number of counts, so that with n flip-flops any dividend up to  $2^n$  can be obtained. When a dividend of N is required, the minimum number of flip-flops (n) can be derived from:  $2^{n-1} < N < 2^n$ .

Pulse feedback is required when  $N \neq 2^n$ , so that  $2^n$  N positions are skipped. The value of  $2^n$  - N gives the indication to which flip-flop in the series the feedback should be applied. In Figs.11 to 15 a few examples of FF1 counters are given. The feedback pulse is supplied to the preceding flip-flops via a pulse gate circuit.

The value of the capacitor in this circuit is determined by the number of flip-flops to which the feedback pulse has to be supplied, viz. approximately 500 pF per flip-flop.

Care should be taken, that the maximum permissible capacitive load of the flip-flop that supplies the feedback pulse is not exceeded. The maximum capacitive loading of the FF1 is 2000 pF. For both Q terminals together when the FF1 is loaded during the negative as well as the positive transient of the pulse. If a 1500 pF series capacitor is used in the feedback path, 500 pF is left for external loading on that terminal (equivalent to another flip-flop). If more than four feedback paths are required, the signal may also be taken from one of the preceding flip-flops.

A disadvantage of this type of counter is that a spurious pulse occurs at the outputs of the flip-flops to which the feedback pulse is applied (see e.g. the output levels of the DC1 as given in the corresponding Data Sheet). If the occurrence of this pulse is not wanted an intermediate gate can be used as indicated in Fig.15.

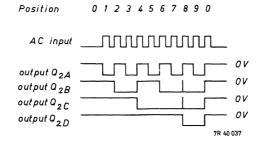

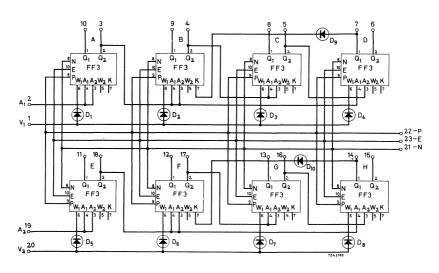

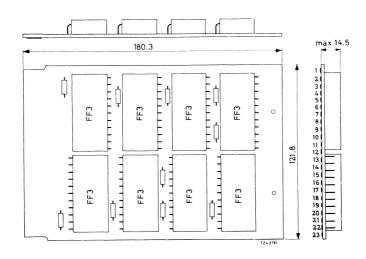

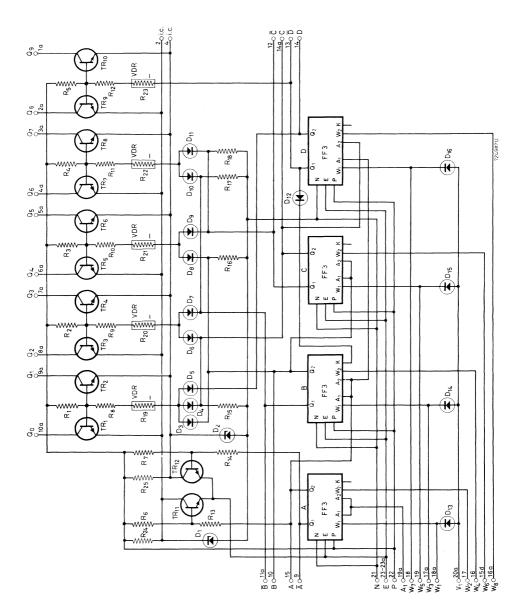

In Fig. 16b a similar type of decade counter is given, but now equipped with flip-flop FF3. With this FF3 however the intermediate gate has been built in the unit itself. The gate condition derived from the  $4^{\rm th}$  flip-flop is connected to the extended gate terminal of the  $2^{\rm nd}$  FF3 via a diode.

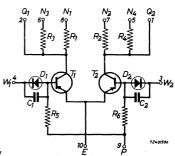

### Shift registers

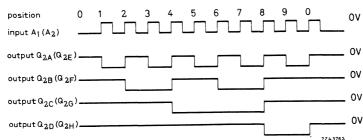

The flip-flops FF2 and FF4 are in principle equivalent to the FF1 and FF3 circuits respectively, with the exception that the built-in input pulse gates can be controlled externally. In this way the switching of the unit, upon reception of a positive going voltage step on its A input is determined by the d.c. levels applied to its G inputs. Thus the binary information presented to the G inputs can be shifted into the flip-flops by the voltage step on A.

The pulse gates are opened by a "negative low" level and closed by a "negative high" level on the corresponding G input.

It is to be noted that for proper working the  $G_1$  and  $G_2$  terminals may not be at a "negative low" level simultaneously.

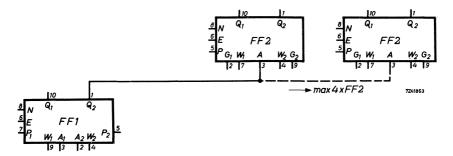

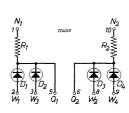

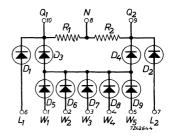

The units 2.PLl and 2.PL2 (Dual Pulse Logic) contain the input gate circuitry of the normal flip-flop FF1 and FF2, and FF3 and FF4 respectively. In this way it is possible by connecting these units to an FF1 and FF3 respectively to obtain a second A input on this unit. In combination with FF2's and FF4's respectively bi-directional shift registers can be made.

In the figures 28 and 29 examples are given of a uni- and a bi-directional shift register.

#### GATES

#### General

As mentioned before, it is immaterial which binary level is denoted by the logic value "0" or by "1", since it has no influence whatsoever on the logic design of a circuit. However, confusion may arise when gate circuits are discussed. Many designers use the words AND and OR for the basic logic functions as well as for the electronic circuits that perform these specific logic operations. The notations AND and OR should, however, be restricted to logic operations, since one gate circuit can perform both the AND and OR operation, dependent on the designation of "0" and "1" to the voltage levels used.

For the above reasons the circuit blocks comprising gate circuits are denoted by "NEGATIVE GATE" and "POSITIVE GATE". The negative gate performs the AND operation on "negative high" signals and the OR operation on "negative low" signals, whilst the positive gate performs the OR operation on a "negative high" signal and the AND operation on a "negative low" signal (see Table below).

|                               | Logic operation performed by |               |  |  |  |  |  |

|-------------------------------|------------------------------|---------------|--|--|--|--|--|

| Signal value "1" assigned to: | Positive gate                | Negative gate |  |  |  |  |  |

| "Negative high" level         | OR                           | AND           |  |  |  |  |  |

| "Negative low" level          | AND                          | OR            |  |  |  |  |  |

### Gate Sequence: Always negative gate - positive gate

Technically it is only possible to drive a positive (P) gate by a negative (N) gate. In the system where the "negative high" signal corresponds to binary "1", the AND-OR sequence is therefore allowed only. This means that every OR-AND combination in the logic diagram should be converted into an AND-OR combination. An example of such a conversion was already given on page A12. It may be convenient to remember that an AND-gate is an OR-gate for the signal of opposite polarity and vice versa. At the outputs of a flip-flopa signal and its complement are simultaneously present, so that no inverter need be used when the signal is taken from a flip-flop.

## Cascading of gates: no more than two

Cascading of more than two gates must generally be avoided. This is due to a large increase of the load on the driving unit when gates are connected in cascade, so that the signal level shift (signal loss) may amount to impracticable values.

An N-N or P-P gate sequence is generally not allowed; such a sequence can, however, always be replaced by one multiple N or P gate respectively.

April 1968 A37

After a signal has passed an N-gate or an N-P gate sequence, it must be restored by an inverter amplifier IA2, an emitter-follower EF2 or a pulse shaper PS1.

### Gates with multiple inputs

In many cases gates with more than three inputs may be required. Such a gate may be composed of any number of 2- or 3-input gates. The following rules should then be observed:

- 1. Interconnect the Q-outputs.

- 2. Connect the negative supply N only once for the whole gate, leaving the other terminals  $\rm N_1$  or  $\rm N_2$  floating.

- 3. If the newly composed gate would have more inputs than actually necessary leave the unused inputs floating.

- 4. A P-gate driven by an N-gate may have 25 inputs at maximum.

- 5. When part of the number of inputs of an N-gate are at "0" level and the other inputs at "1" level, the supply of the leakage currents of the diodes that are cut-off is distributed over the inputs at zero level. (The maximum of this leakage current is  $40~\mu\rm A$  for every input in the "1" position.) This may give rise to a considerable increase of the load at these inputs. (See also the corresponding Data Sheets.)

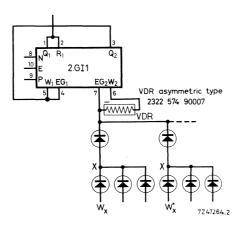

Examples of multiple-input gates are given in Figs. 18 to 22.

#### Positive gates

The rules given above under 1, 2 and 3 for N-gates also apply to P-gates. It must be noted, however, that, unlike the N-gate, the P-gate may load the driving stage at both binary levels.

The terminals  $P_1$  or  $P_2$  of the P-gate may be leftfloating when the following stage is already equipped with a resistor from the input to the positive supply voltage. This is the case with the inverter-amplifiers IA1 and IA2.

When a P-gate is driven by an N-gate, the number of P-gate inputs may not exceed 25. On the other hand, an N-gate may be loaded by only one P-gate.

## More than one gate driven by more than one flip-flop

The Loading Table indicates the number of gates with which the other circuit blocks may be loaded. It should be remembered, however, that an N-gate only presents a "load" if it produces a "negative low" signal at its output. When several gate inputs carry a "negative low" signal simultaneously, the load is divided among the driving sources. When a number of gates is driven by a number of flip-flops, it may therefore be allowed to connect each flip-flop to a number of gates greatly exceeding that given in the Loading Table. That is because the

effective loading may be far less than the actual number of gates. This must be checked carefully for every possible state of the circuit.

The same applies, as a matter of course, for other driving sources.

### Voltage levels in gate circuits

Due to the voltage drop across the diodes of the gates, a voltage level shift will occur in every gate, so that the signal, after having passed one or more gates, is no longer in agreement with the level standards of the input signals. In the Loading Table this effect has already been taken into account. When a combination of gates that is not covered by the Loading Table must be used, the following information should be borne in mind:

- 1. A germanium diode in an N-gate causes a level shift of -0.1 V to -0.5 V 1).

- 2. A silicon diode in a P-gate causes a level shift of  $\pm 0.4$  V to  $\pm 1.0$  V  $^{1}$ ).

- 3. A common emitter stage needs -0.2~V to -0.4~V on its base for the conducting state and approximately +0.2~V for its cut-off state  $^1$ ).

- 4. The collector-voltage level of a conducting common emitter stage ("0" output) has to be taken as -0.05 V to -0.2 V  $^{1}$ ).

### Current in gate circuits

Since the forward resistance of a conducting diode and the input impedance of a common emitter transistor, when driven into the conducting state, is very low, a strong gate current may occur, which may overload or damage the circuit elements.

On the other hand, the generator impedance of an "open" gate is high, resulting sometimes in too low an available driving current for a given stage. When applying other combinations, such as given in the examples below or in the Loading Table, these points have therefore to be investigated.

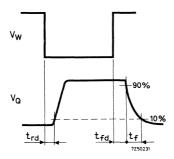

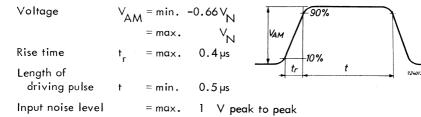

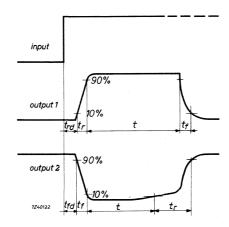

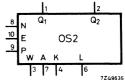

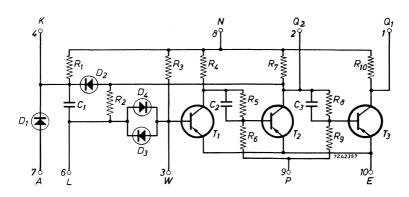

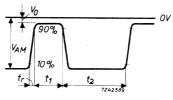

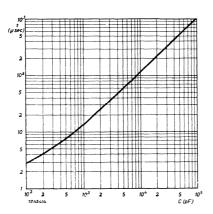

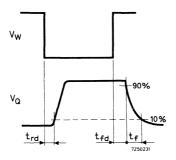

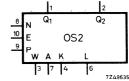

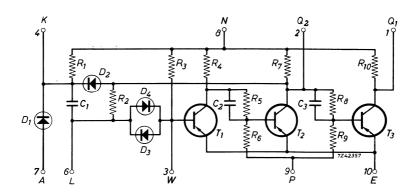

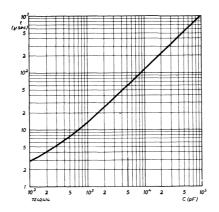

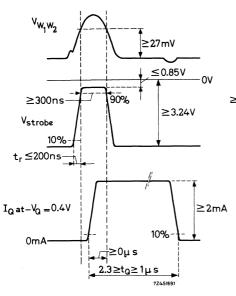

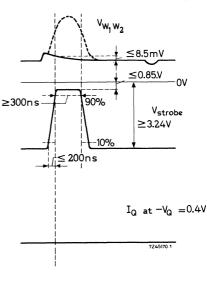

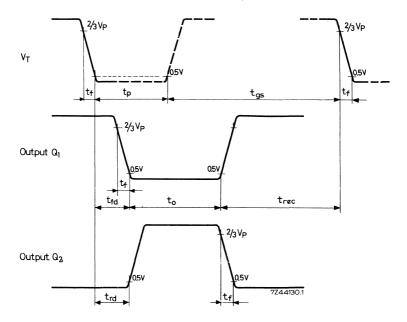

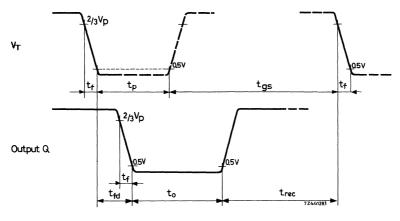

#### ONE-SHOT MULTIVIBRATORS OS1 AND OS2

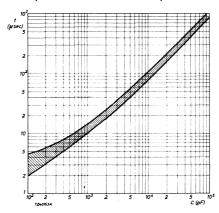

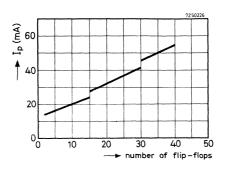

The one-shot multivibrator OS1 is intended to produce a pulse of definite length for providing a time delay. Both a positive- and a negative-going pulse are available at the outputs. It should be noted that at the  $Q_2$  terminal the maximum permissible load current is appreciably lower than that at the  $Q_1$  terminal, whilst the rise time of the pulse at the  $Q_2$  terminal is higher than that at the  $Q_1$  terminal.

<sup>1)</sup> Related to the type of semiconductor as used in the circuit blocks and dependent on the current flowing through the diodes. In calculations on the levels the most unfavourable limit of the values given has to be applied.

It is not recommended to use the OS1 for delays that exceed the values given in the graph (see Data Sheets), i.e. longer than 1 ms, since in this case the OS1 is more sensitive to spurious signals induced on the supply line. Moreover, the use of electrolytic capacitors would be required, which are less stable during life and may show a considerable leakage current. For long delays it is therefore recommended to use a frequency divider fed from a fixed frequency, such as the a.c. mains.

When the OS1 is used for long delays the negative supply line should be bypassed close to the unit by a large capacitor.

The one-shot multivibrator OS2 has considerable advantages above the OS1 in particular with respect to the maximum permissible load current on both Q-terminals whilst the rise time of the pulses derived from  $\rm Q_1$ - and  $\rm Q_2$ -terminal are equal (see Data Sheets).

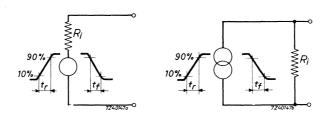

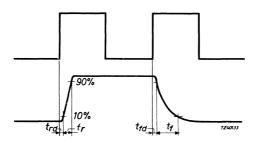

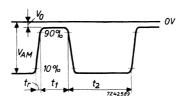

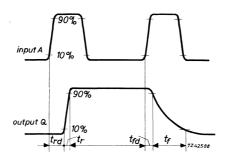

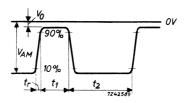

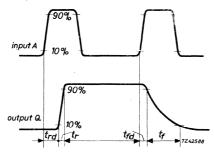

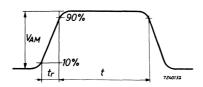

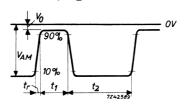

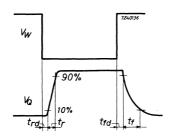

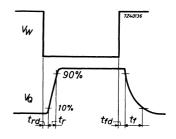

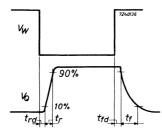

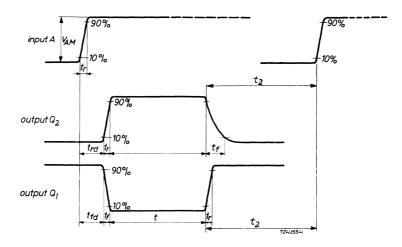

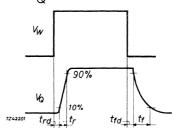

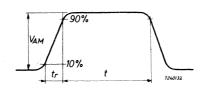

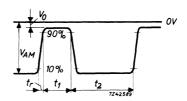

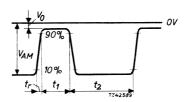

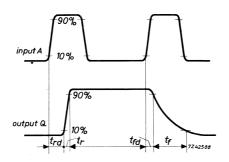

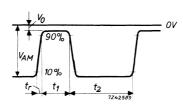

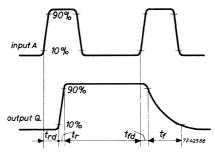

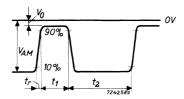

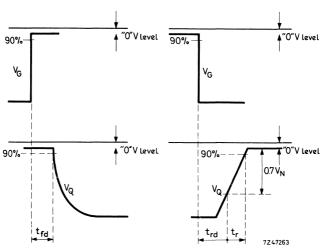

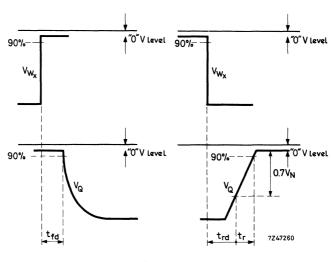

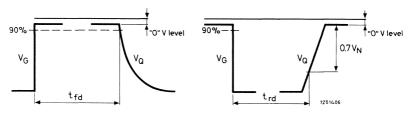

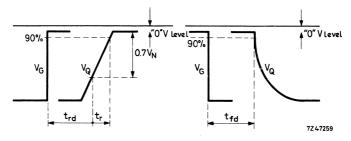

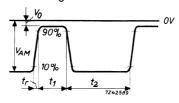

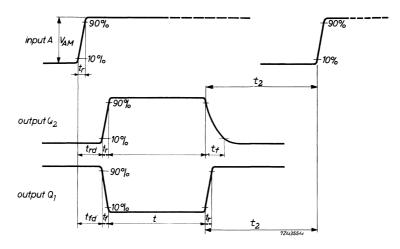

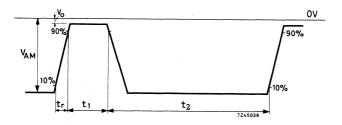

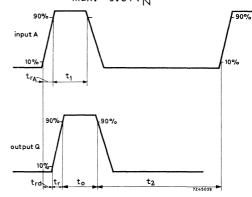

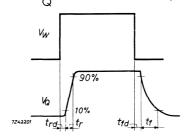

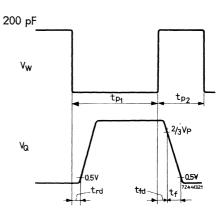

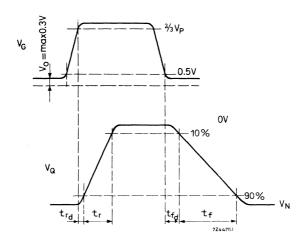

#### TRANSIENTS AND DELAY TIMES

Although all circuit blocks function properly in any permitted sequence at frequencies up to 100 kHz, practical considerations may cause a reduction of this speed. This may happen when the total delay in a chain of cascaded circuits is too long for the specific application. It must be examined on the basis of the switching times and delay times as given in the Data Sheets.

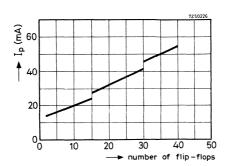

As a typical example an 8-stage binary counter with flip-flops FF1 will be considered. From the Data Sheet it follows, that in this counter a total dolay of 8. ( $t_{\rm rd}+t_{\rm r}$ ) = 8.8  $\mu$ s occurs. If the output signal of the 8th flip-flop should coincide with the input pulse of the counter for at least 2  $\mu$ s, it is required for this input pulse to have a duration of minimum 8.8  $\mu$ s + 2  $\mu$ s = 10.8 $\mu$ s. This requirement reduces the maximum operational frequency in the application at issue to approximately 46 kHz.

The transients in a loaded switching circuit can be calculated from the output data given in the Data Sheets.

The intrinsic switching times given in these data always apply to the unloaded condition. Generally they remain unaffected under conditions of resistive loading, whereas a capacitive load increases the switching times.

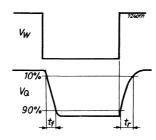

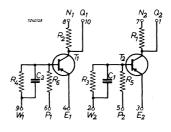

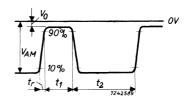

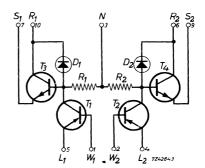

Fig. 58 Equivalent diagrams of active circuit blocks

A40

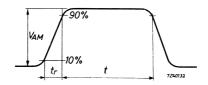

The actual switching time of a loaded circuit can easily be calculated from the equivalent diagrams shown in Fig. 58. The unit can be represented by a step voltage or current source in combination with the internal (output) impedance of the unit. The value of this output impedance is given in the Data Sheet of the unit under consideration. The total rise time and fall time of the output voltage are approximately equal to:

$$t_{\rm r}$$

tot =  $\sqrt{t_{\rm r}^2 + (2.2 \ \tau)^2}$  and  $t_{\rm f}$  tot =  $\sqrt{t_{\rm f}^2 + (2.2 \ \tau)^2}$

in which:

$t_r$  = the intrinsic rise time of the unit,

$t_f$  = the intrinsic fall time of the unit,

$\tau$  = the time constant of the load and internal resistance of the unit.

When the load consists of the parallel circuit of a resistive part  $R_1$  and a capacitive part  $C_1$  (which will mostly be the case):

$$\tau_1 = \frac{R_1 \cdot R_i}{R_1 + R_i} \cdot C_1,$$

in which  $R_i$  is the internal resistance of the unit.

# =

# ELECTRICAL INTERFERENCE AND APPROPRIATE COUNTER-MEASURES

#### Introduction

In industrial applications of transistorized electronic equipment sometimes troubles are encountered caused by interfering signals.

In designing equipment in which circuit blocks containing transistorized circuits are applied it is very important to pay due attention to the various possible sources of interference.

Interfering signals, mostly present during a short interval, can temporarily disturb the regular signals. In sequential circuits e.g. a one-shot multivibrator or flip-flop circuit (with a memory function), the interfering signal may be stored as a piece of information. In industrial equipment with transistor circuits interference is often produced by the switching of electro-magnetic loads, such as: relays, clutches, electro-magnetic valves, motors, transformers, welding apparatus, etc..

In almost all cases, however, these interference problems can be fully overcome by observing a number of simple design rules.

Most of these rules refer to the circuit lay-out, the wiring etc., so that they can only be applied efficiently and in the most effective way, when they have been duly accounted for at the outset of the development. Any correction afterwards is costly, time consuming and often even impossible.

# ${\bf Transistors\ versus\ Tubes\ and\ Relays\ in\ Control\ Equipment\ with\ respect\ to\ Interference}$

Relay systems which operate at a very high power level are by nature very insensitive to interference.

In electronic control circuits a much lower signal power level is applied which consequently can be easily upset by interfering signals that are caused by external stray fields. In such cases special precautions are required.

It is not generally recognised that thermionic tube and transistor equipment behave quite differently in this respect.

In tube circuitry with higher voltage levels mostly higher interference levels are allowed. Because of the rather high impedance of the signal lines most interference is of capacitive nature, a capacitive screening of the signal lines is in many cases sufficient.

Transistor circuitry mostly operates at a much lower voltage level and has a lower impedance. Here a relatively higher sensitivity to magnetic stray interferences can be found. In these circuits a simple capacitive screening only solves a small part of the problems.

April 1968 | A43

The sections below contain a survey of various kinds of interference and indications as to their elimination or reduction.

Essentially there are two principal rules to be borne in mind:

- A. eliminate the sources of interference or reduce their effect

- B. make the circuit itself insensitive to the remaining interference signals to the highest possible degree.

The latter rule is most important because:

- during design and development the future working circumstances are often not known,

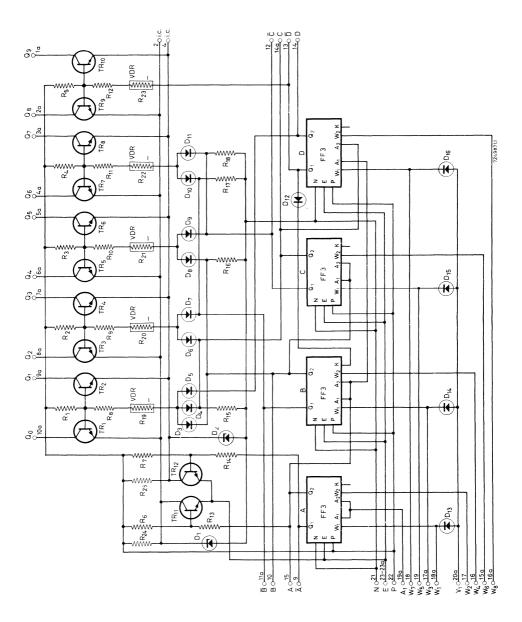

- a complete suppression of interference is mostly not possible.

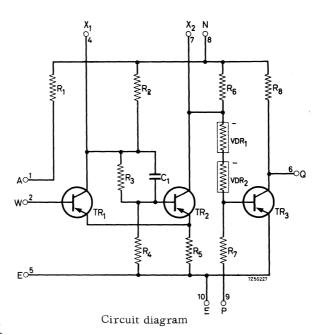

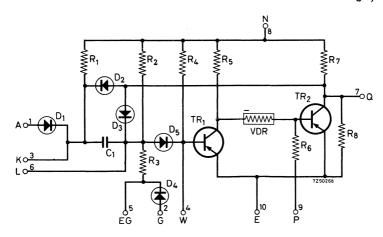

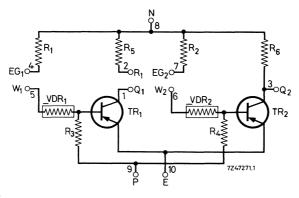

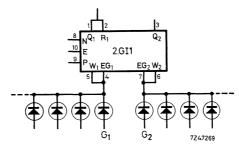

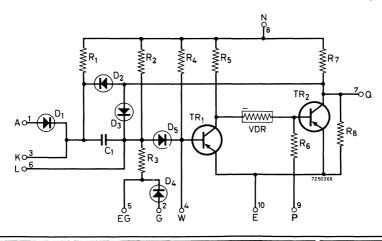

#### A. SUMMARY OF POSSIBLE INTERFERENCE SOURCES AND COUNTER-MEASURES

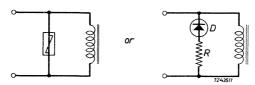

- Spark extinction at switch contacts of motors and peak voltage suppression at inductive loads.

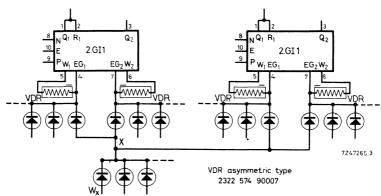

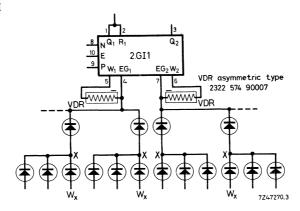

- 1.1 Bridging the contacts by means of a voltage-dependent resistor (VDR).

The peak voltage and the resulting arcing between the contacts will be reduced.

1.2 Bridging the contacts by means of a capacitor/resistor combination.

The capacitor reduces the voltage when the contact is opened. The resistor reduces the discharge current of the capacitor, when the contact is closed.

## ELECTRICAL INTERFERENCE AND APPROPRIATE COUNTER-MEASURES

1.3 Bridging the load itself by a voltage dependent resistor or diode-resistor combination.

2.  $\underline{\text{Dust}}$  on (or contamination of) the electro-magnetic power contacts.

A proper dust sealing solves this problem.

3. Incorrect positioning of possible interference sources.

Keep components and/or units which can act as interference sources, separated from the circuits that are sensitive to interference. Further improvements can be obtained by placing a metal shielding between these parts of the equipment.

- 4. Interference caused by improper wiring.

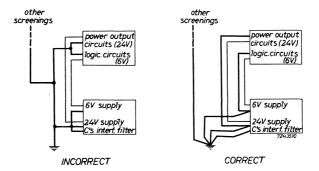

- 4.1 Wiring of earth lines

The principle is that the earth lines of the two supplies should be kept as far apart as possible. This holds in particular for the earth line of power transistors. The drive currents of these transistors, which are also sent through the earth lines, are rather high and can cause voltage differences.

To reduce the chance of interference it is preferable to keep the length of earth lines as short as possible and to use wire of adequate diameter. All earth lines must be connected separately to one common earth point on which also the chassis and other screenings are earthed.

- 4.2 Wiring that forms the connection to electro-magnetic loads, and leads that carry large currents, must be kept separated from the signal leads, which may transfer the interfering signals to the circuits that are sensitive to interference.

- 4.3 Signal carrying lines should be kept as short as possible and loops avoided. As screening material of these lines iron or steel must be used, a steel-armoured cable is very suitable for this purpose.

Furthermore it is preferable to screen signal lines, which are connected to triggered circuits, from other lines in this cable.

The earthing of the steel sheath as well as that of the separate line screening must be done at the common earth point of the chassis.

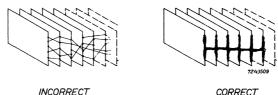

4.4 Decrease the wiring area

Example: wiring of a bank of printed-wiring connectors.

However, the wiring connected to inductive loads (drive lines for relays etc. or generally high pulse current lines) must be kept apart, with their own earth return.

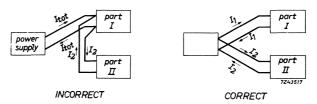

5. Common impedance of two or more parts of an equipment.

If, for instance, two parts of an equipment are connected to the same power supply, a reduction of the common impedance can be obtained by using separate supply lines.

Further reduction can be achieved by using:

- a stabilised power supply (low internal impedance)

- separate power supplies for each part of the equipment.

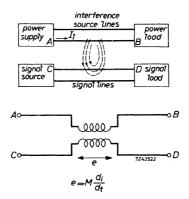

## 6. Electro-magnetic coupling between signal and/or supply lines.

This coupling can be reduced by the following measures:

- reduce the magnetic field by twisting the interference source lines;

- cancel the induced voltage by twisting the signal lines;

- reduce the coupling magnetic field by increasing the distance between interference source lines A-B and signal C-D;

- reduce the coupled magnetic field by a shield of a ferromagnetic material;

- reduce the coupled magnetic field by decreasing the length of the interfering lines;

- choose circuit parameters in order to: decrease signal load impedance decrease magnitude and frequency of interfering currents;

- cancel the induced voltage by crossing the wires at right angles.

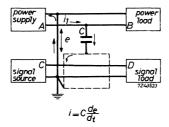

## 7. Electro-static coupling

This coupling can be reduced by the following measures:

- use an electrically conductive shield as shown in the figure. The capacitance C short-circuits the leakage current to earth, by-passing lead CD;

- increase the distance between the wires;

- decrease the dielectric constant of medium between wires;

- decrease the diameter of the conductors;

- decrease the length of the wires.

#### B. MEASURES TO REDUCE OR ELIMINATE INDUCED INTERFERENCES

It should be noticed that induced interfering pulses may upset the functioning of systems by entering the logic circuits via:

- 1 the mains supply

- 2 induction on the low-voltage supply lines to the circuitry (included earth lines)

- 3 induction on lines which transmit the driving signals.

Generally, it is of great importance to place the transistor circuitry in a well-earthed metal case or frame. Metal sheet with a thickness of 1 mm will serve the purpose. The material must have a proper permeability to ensure sufficient magnetic screening, e.g. iron or steel (not aluminium).

Interference, which is introduced via the ways 1, 2 or 3 can be suppressed by:

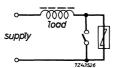

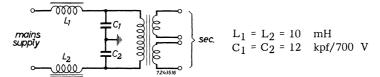

1.1 A filter in the primary of the mains transformer.

When this is still inconclusive, a third capacitor can be connected in parallel with the primary of the transformer.

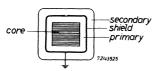

1.2 An electrostatic shield between primary and secondary of the mains transformer. This shield consists of a layer of copper foil which is connected to earth.

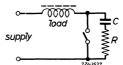

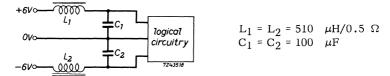

2.1 A filter in the low voltage supply lines of the logical circuitry.

Care should be taken that only the low-level logical circuits are supplied via this filter, as otherwise the current variations will become excessive.

## ELECTRICAL INTERFERENCE AND APPROPRIATE COUNTER-MEASURES

2.2 It is sometimes necessary to use an extra filter in the  $-6\,V$  supply line close to the circuits, that are sensitive to interference, e.g. the one-shot multivibrator OS.

- 3. If signals are to be transmitted from one part of the equipment to another the following rules must be observed:

- improve the signal-to-noise (interference) level on the line by raising the voltage level of the signal;

- apply low-pass filters at all equipment inputs, cutting off signals of a frequency higher than the maximum signal frequency;

- prefer "level" (d.c.) signal transmission to pulse transmission (interference is often intermittent and of short duration).

A few circuits are given below:

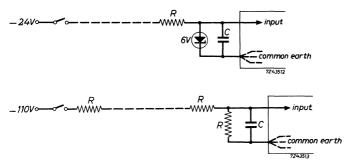

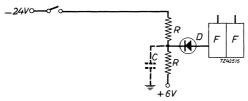

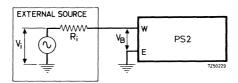

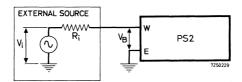

3.1 Electro-mechanical contact, external supply:

3.2 External contact, supply from the equipment:

Note: apply this filtering particularly when the supply, common to the transistor circuits, is used for the line as well. Choose the resistors such that overloading the power supply or transistorized circuitry at short-circuit conditions of the line is avoided.

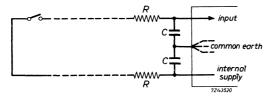

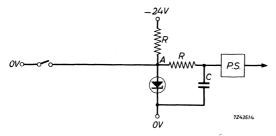

3.3 Transmission of lower-speed timing signals between equipment parts:

After the RC-network has been passed, the signal form is restored by a pulse shaper.

Note the delay in pulse transmission caused by the RC-network.

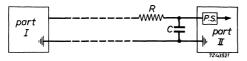

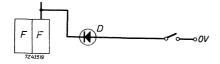

3.4 Remote setting of a flip-flop from a negative voltage source.

When the switch is open, the diode is non-conducting, because of the  $+6~\mathrm{V}$  threshold voltage.

The diode remains blocked for positive interference pulses, whereas for negative pulses to become effective the amplitude must be at least comparable with the threshold voltage.

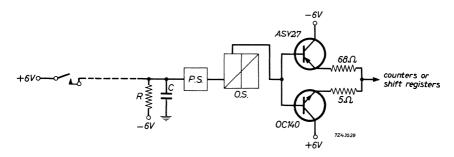

3.5 An almost similar effect can be obtained with the following circuit, intended for driving pulse shapers or inverters.

The voltage at point A will be -6 V when the switch is open. Negative interference pulses will not influence the state of the pulse shaper; positive pulses are short-circuited by the conducting Zener diode. When the switch is closed, point A will become 0 V, so that the pulse shaper is caused to change its state.

A50 April 1968

## ELECTRICAL INTERFERENCE AND APPROPRIATE COUNTER-MEASURES

### 3.6 Remote setting of a flip-flop from a voltage of 0 V.

By closing the switch, the flip-flop is forced to change its state. This method has the advantage, that switch and line are not connected to the sensitive, high-impedance base input.

### 3.7 Avoidance of contact bouncing

When a shift register or counter must be operated by an electro-mechanical contact, it is essential that the contact bouncing should be avoided. This can be done by means of a one-shot multivibrator of which the pulse has the required characteristics.

To reduce the time in which interference can be induced (switch open) a break contact is used. The one-shot multivibrator operates every time the switch is opened.

| , |  |  |  |  |  |

|---|--|--|--|--|--|

|   |  |  |  |  |  |

|   |  |  |  |  |  |

## LOADING TABLE

If not indicated separately the N and P terminal(s) of each unit are connected to  $v_N$  respectively  $v_P$ . (v\_N = -6 V  $\pm 5$  %,  $v_P$  = +6 V  $\pm 5$  %.)

|                      |                                           | ·                   |      |                      | r                              |                  |                  |                   |                                                  |                  |                                                     |                                                     |   |   |                  |                       |

|----------------------|-------------------------------------------|---------------------|------|----------------------|--------------------------------|------------------|------------------|-------------------|--------------------------------------------------|------------------|-----------------------------------------------------|-----------------------------------------------------|---|---|------------------|-----------------------|

| preceding<br>unit or |                                           | driving<br>unit     |      |                      | maximum number of driven units |                  |                  |                   |                                                  |                  |                                                     |                                                     |   |   |                  |                       |

|                      | preceding                                 |                     | 11   | via                  | FF1                            |                  |                  | FF2               | т                                                | FF3              |                                                     | т——                                                 |   |   |                  |                       |

| chain of<br>units    |                                           | type                | out- | Via                  | w                              | A                | w                | A                 | G                                                | w                | Al<br>or                                            | A1<br>+                                             |   |   |                  |                       |

| u                    | units                                     |                     | put  |                      |                                |                  | L.               |                   |                                                  |                  | A2                                                  | A2                                                  |   |   |                  |                       |

|                      |                                           | FFI                 | Q    |                      | 11)                            | 49)              | 1 <sup>1</sup> ) | 49)               | 2 <sup>10</sup> )                                | 1 <sup>1</sup> ) | 2 <sup>10</sup> )                                   | 2 <sup>10</sup> )                                   |   |   |                  |                       |

|                      |                                           | FF2                 | Q    |                      | ~11)                           | 110)             | 1 <sup>1</sup> ) | 110)              | 2 <sup>10</sup> )                                | 1 <sup>1</sup> ) | 110)                                                | 1 <sup>10</sup> )                                   |   |   |                  |                       |

|                      |                                           | FF3                 | Q    |                      | 11)                            | 5 <sup>9</sup> ) | 1 <sup>1</sup> ) | 5 <sup>9</sup> )  | 210)                                             | 11)              | 310)                                                | 3 <sup>10</sup> )                                   |   |   |                  |                       |

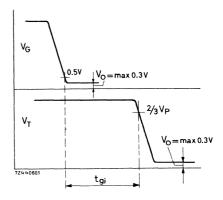

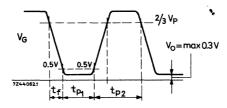

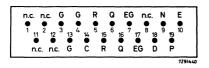

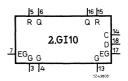

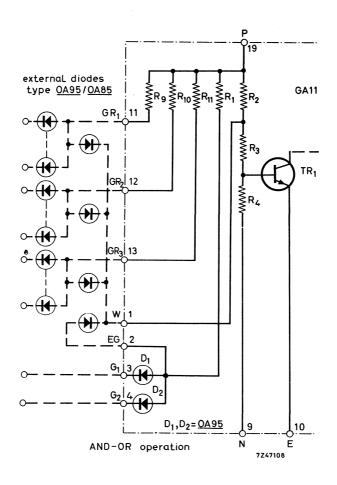

|                      |                                           | FF4                 | Q    |                      | 11)                            | 5 <sup>9</sup> ) | 11)              | 5 <sup>9</sup> )  | 2 <sup>10</sup> )                                | 11)              | 310)                                                | 310)                                                |   |   |                  |                       |